Intel® Quartus® Prime Pro Edition User Guide: Design Compilation

A newer version of this document is available. Customers should click here to go to the newest version.

2.3.2.1.2. Applying the SDC-on-RTL Constraints

SDC-on-RTL requires you to perform the DNI-based Analysis and Elaboration on your design before applying the constraints, which means that SDC-on-RTL SDC files are read during elaboration. If you modify the constraints after Analysis and Elaboration, then you must rerun Analysis and Elaboration.

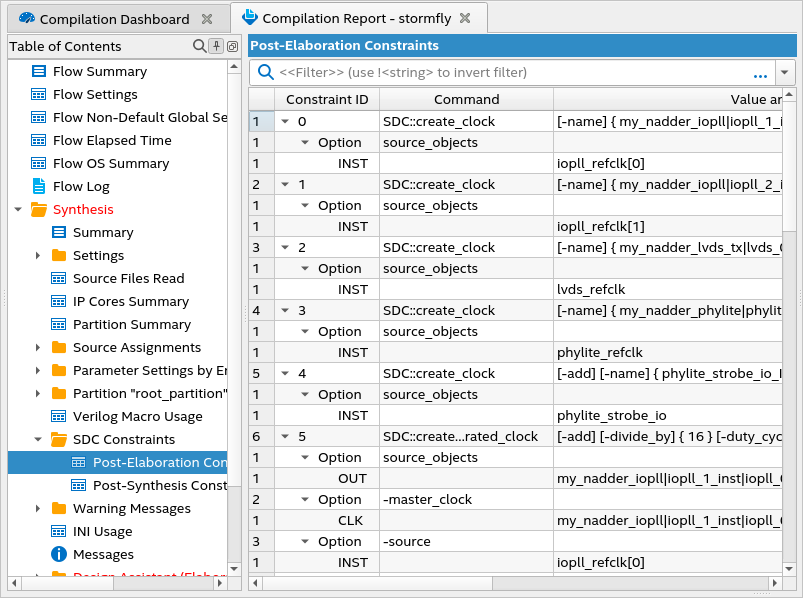

During the Analysis and Elaboration, quartus_syn reads all SDC-on-RTL SDC files and applies constraints to your design netlist. The order in which the files are listed in the QSF defines the reading order. Once this compilation stage completes, you can inspect the constraints in multiple ways. For more information, refer to Inspecting SDC-on-RTL Constraints and Types of SDC Files Used in the Intel Quartus Prime Software.

The constraints are stored in the internal Intel® Quartus® Prime software netlist. As the compilation flow progresses, various compiler optimizations keep the constraint targets updated. This permits a write once, use anywhere methodology for the constraints.

Once you are satisfied with the constraints, you can run Synthesis and Early Timing Analysis stages from the compilation dashboard. Synthesis converts the elaborated netlist into the node netlist for mapping to device resources. When Synthesis runs, you can observe that the SDC constraints are processed and propagated by the Synthesis tool, and eventually, these constraints propagate into the Early Timing Analysis stage.