AN 836: RapidIO II Reference Design for Avalon-ST Pass-Through Interface

ID

683197

Date

12/18/2017

Public

1.4.3. Running the Design

When the board is set up and the FPGA is programmed, you can start running the design:

- Invoke the system console. This can be done at the Nios® II command shell or from the Intel® Quartus® Prime software GUI.

- In the command window, change your directory to system_console by typing the following command :

cd system_console - Execute the following commands at the system console:

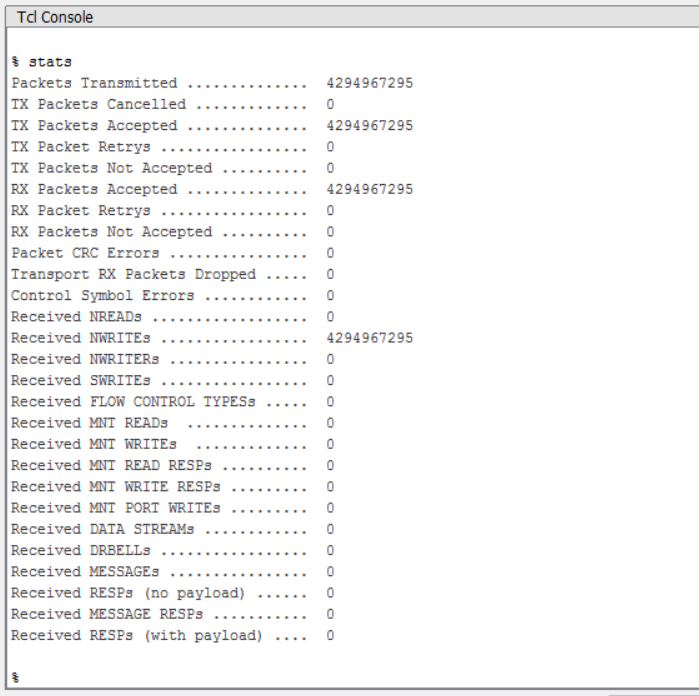

source main_run.tcl cfig link cstats stats start stats - The traffic generator module starts to generate RapidIO NWRITE transactions with a default payload of 64 bytes. The default number of NWRITE transactions is 0xFFFFFFFF (4,294,967,295 decimal). You can stop the traffic generator by entering the stop command. The generated RapidIO transactions are being received at the traffic checker module since all the traffic is looped back through the FMC Loopback Card.

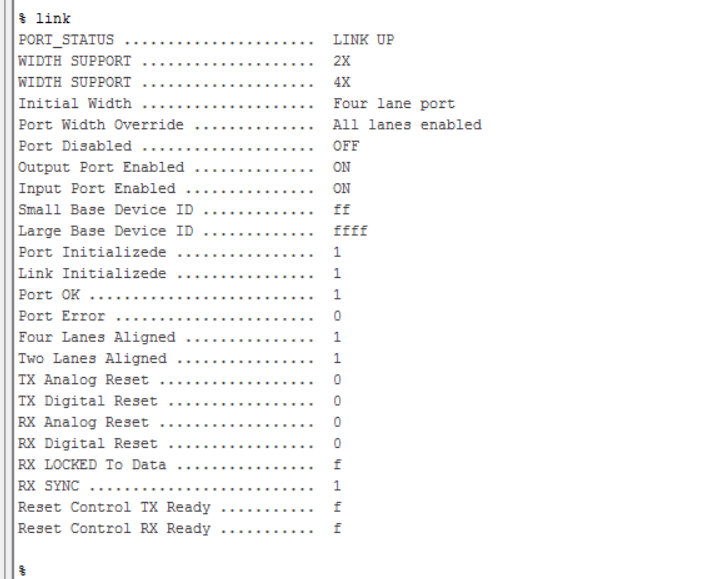

You can view the transactions transmitted and received counts as well as other statistics by entering the link and the stats commands at the system console.Figure 7. Link Command Execution

Figure 8. Stats Command Execution

Figure 8. Stats Command Execution

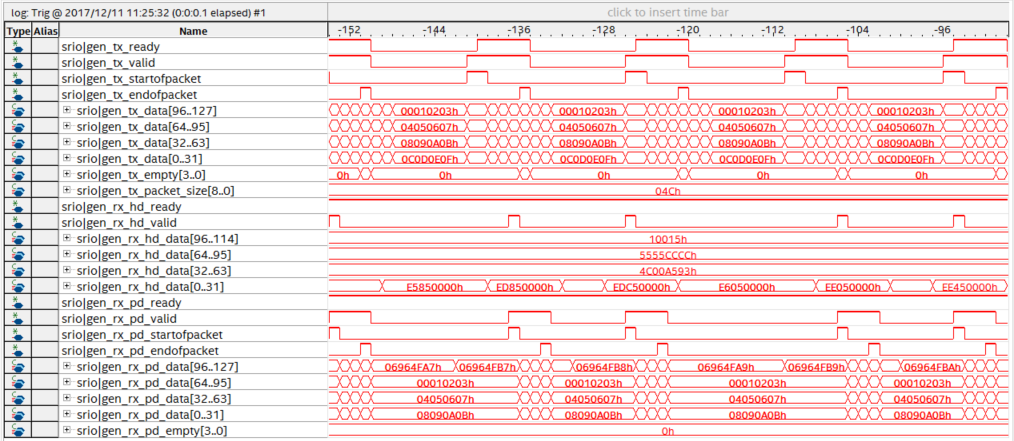

- Use Signal Tap to view the packet exchange. This reference design includes the Signal Tap file srio2.stp which monitors the gen_tx and the gen_rx interfaces of the RapidIO Avalon® -ST pass-through interface. The figures below shows the Signal Tap activity.

Figure 9. auto_signaltap_1

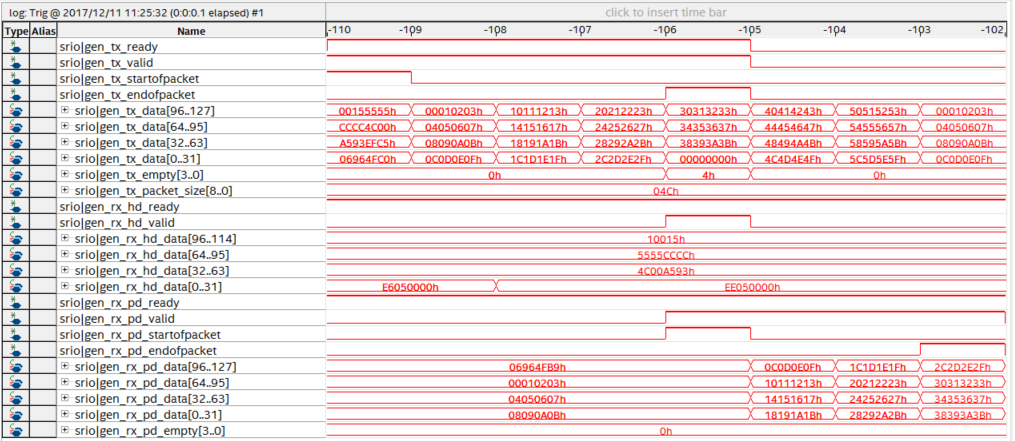

Figure 10. auto_signaltap_2

Figure 10. auto_signaltap_2

Related Information