Developer Guide

FPGA Optimization Guide for Intel® oneAPI Toolkits

A newer version of this document is available. Customers should click here to go to the newest version.

Handshaking Between Clusters

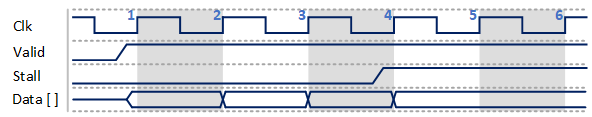

By default, the handshaking protocol between clusters is a simple stall/valid protocol. Data from the upstream cluster is consumed when the stall signal is low, and the valid signal is high.

Hyper Optimized Handshaking

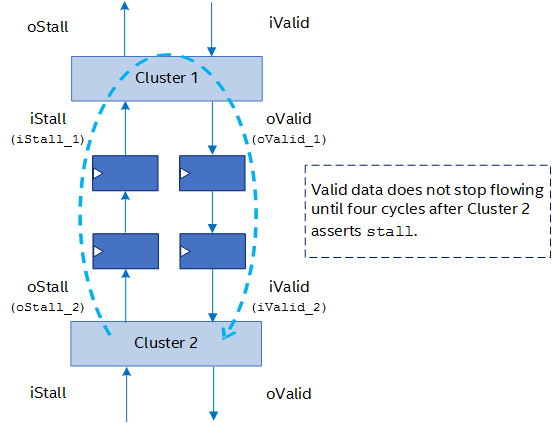

If the distance across the FPGA between these two clusters is large, handshaking may become the critical path that affects peak fMAX in the design. To improve these cases, the Intel® oneAPI DPC++/C++ Compiler can add pipelining registers to the stall/valid protocol to ease the critical path and improve fMAX. This enhanced handshaking protocol is called hyper-optimized handshaking.

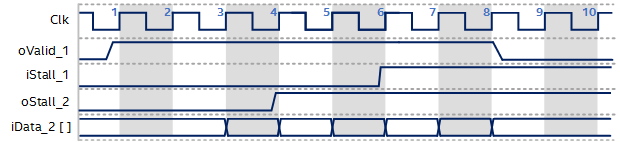

The following timing diagram illustrates an example of upstream cluster 1 and downstream cluster 2 with two pipelining registers inserted in-between:

Hyper-optimized handshaking is currently available only for the Intel Agilex® 7 and Intel® Stratix® 10 device families.