A newer version of this document is available. Customers should click here to go to the newest version.

2.1. Clock Signals

2.2. Reset Signals

2.3. TX MII Interface (64b/66b)

2.4. RX MII Interface (64b/66b)

2.5. Status Interface for 64b/66b Line Rate

2.6. TX Interface (8b/10b)

2.7. RX Interface (8b/10b)

2.8. Status Interface for 8b/10b Line Rate

2.9. Serial Interface

2.10. CPRI PHY Reconfiguration Interface

2.11. Datapath Avalon Memory-Mapped Interface

2.12. PMA Avalon Memory-Mapped Interface

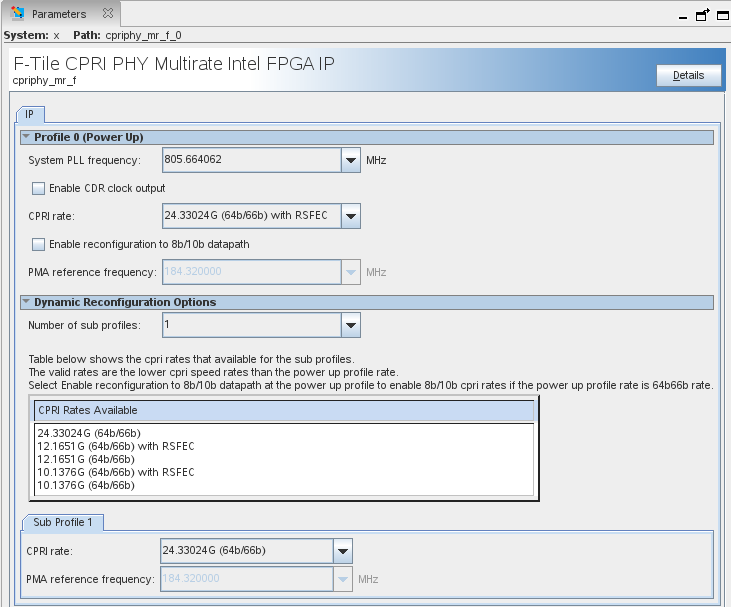

3. Parameters

You customize the IP core by specifying parameters in the IP parameter editor.

Figure 5. IP Parameter Editor

| Parameter | Supported Values | Default Setting | Description |

|---|---|---|---|

| Profile 0 (Power Up) | |||

| System PLL Frequency |

|

805.664062 MHz | Select the System PLL frequency for your IP. |

| Enable CDR Clock Output |

|

Off | Turn on this parameter to enable CDR clock output. You can enable this feature only if the transceiver is placed at FGT transceiver Quad 3 or Quad 2 location. |

| CPRI Rate |

|

24.33024G (64b/66b) with RS-FEC | Selects the CPRI data rate. The hard RS-FEC block is included in the core if you select 10.1376, 12.1651, and 24.33024 Gbps (64b/66b) with the RS-FEC option. |

| Enable Reconfiguration to 8b/10b Datapath |

|

Off | Turn on this parameter if you plan to reconfigure the CPRI line rate of your channels from 64b/66b datapath rates to 8b/10b datapath rates at run-time. If this option is not enabled, the CPRI IP core uses fewer resources, and you cannot change to 8b/10b datapath rates at run-time. |

| Dynamic Reconfiguration Options | |||

| Number of Sub Profiles | 1 to 11 | 1 | Select the number of sub profiles. |

| CPRI Rate for Sub Profile |

|

24.33024G (64b/66b) with RS-FEC | Selects the CPRI data rate for the sub profile. |

| PMA Reference Frequency |

|

184.32 MHz | Only one value of the reference clock frequency is supported for each CPRI line rate:

|