Configuration via Protocol (CvP) Implementation in V-series FPGA Devices User Guide

ID

683889

Date

9/04/2020

Public

5.1. Understanding the Design Steps for CvP Initialization Mode

5.2. Understanding the Design Steps for CvP Initialization Mode with the Revision Design Flow

5.3. Understanding the Design Steps for CvP Update Mode

5.4. Bringing Up the Hardware

5.5. CvP Debugging Check List

5.6. Known Issues and Solutions

5.2.1. Downloading and Generating the High Performance Reference Design

5.2.2. Workaround for a Known Issue with Transceiver Reconfiguration Controller IP Core

5.2.3. Creating an Alternate user_led.v File for the Reconfigurable Core Region

5.2.4. Setting up CvP Parameters for CvP Initialization Mode

5.2.5. Creating CvP Revisions of the Core Logic Region Using the CvP Revision Design Flow

5.2.6. Compiling both the Base and cvp_app Revisions in the CvP Revision Design Flow

5.2.7. Splitting the SOF File for the CvP Initialization Mode with the CvP Revision Design Flow

5.3.1. Downloading and Generating the High Performance Reference Design

5.3.2. Workaround for a Known Issue with Transceiver Reconfiguration Controller IP Core

5.3.3. Creating an Alternate user_led.v File for the Reconfigurable Core Region

5.3.4. Setting up CvP Parameters for CvP Update Mode

5.3.5. Creating CvP Revisions of the Core Logic Region Using the CvP Revision Design Flow

5.3.6. Compiling the Design for the CvP Update Mode

5.3.7. Splitting the SOF File for the CvP Update Design Mode

5.3.8. Splitting the SOF File for the CvP Update Mode with the CvP Revision Design Flow

6.3.1. Altera-defined Vendor Specific Capability Header Register

6.3.2. Altera-defined Vendor Specific Header Register

6.3.3. Altera Marker Register

6.3.4. CvP Status Register

6.3.5. CvP Mode Control Register

6.3.6. CvP Data Registers

6.3.7. CvP Programming Control Register

6.3.8. Uncorrectable Internal Error Status Register

6.3.9. Uncorrectable Internal Error Mask Register

6.3.10. Correctable Internal Error Status Register

6.3.11. Correctable Internal Error Mask Register

5.1.4. Splitting the SOF File for the CvP Initialization Design Mode

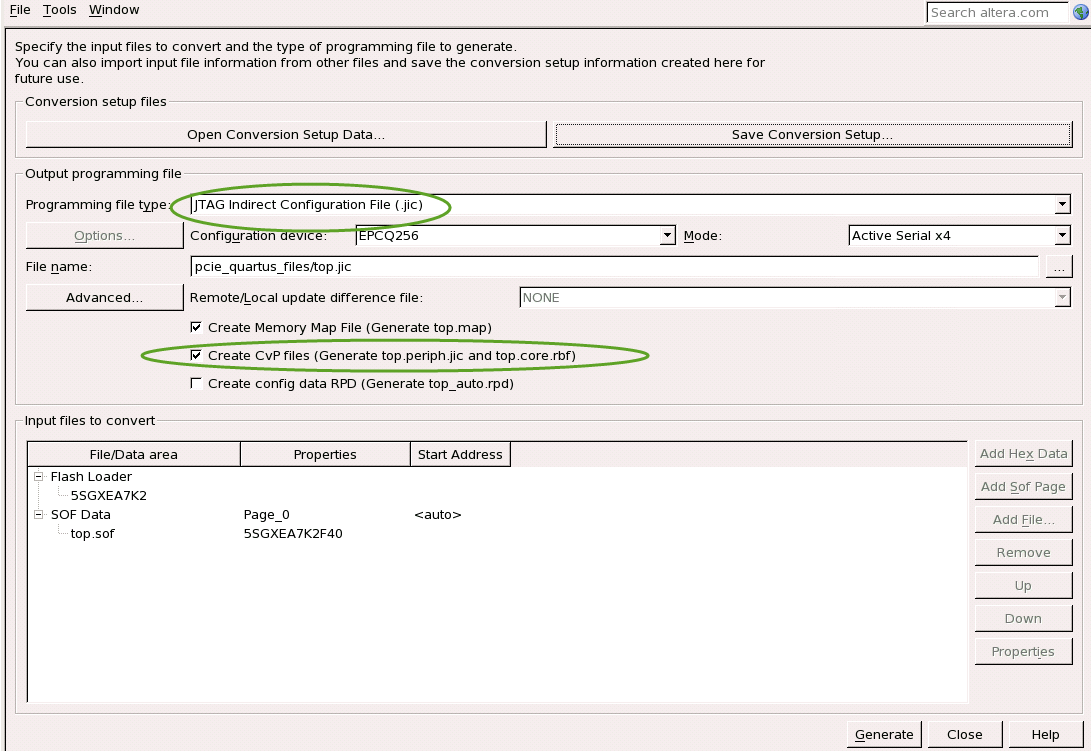

Follow these steps to split your .sof file into separate images for the periphery and core logic.

- On the File menu, select Convert Programming File.

- Under Output programming files to convert, specify the options in the following table.

Table 11. CvP Initialization Output Programming Files Settings Parameter

Value

Programming file type

JTAG Indirect Configuration File (.jic)

Configuration device

EPCQ256

Mode

Active Serial x4

File name

Browse to and select the ./pcie_quartus_files/ directory. Type the file name top.jic . Then click Save.

Create Memory Map File

Turn this option on.

Create CvP files

Turn this option on. This box is greyed out until you specify the SOF Data file under Input files to convert.

- Under Input files to convert, specify the options in the following table:

The following figure illustrates the options that you specified.

Table 12. CvP Initialization Input Files to Convert Settings Parameter

Value

Click Flash Loader

Click Add Device and select Stratix V and then 5SGXEA7K2, and click OK.

Click SOF Data

Click Add File and navigate to ./pcie_quartus_files/top.sof. If you specified a compressed or encrypted bitstream in the Device and Pin Options dialog box, you must specify the same options for Conversion Programming File window. To enable these settings, click top.sof. Then click Properties and check the appropriate boxes. Mode

Active Serial x4

Figure 20. CvP Initialization Mode: Convert Programming File Settings

- Turn on the Create CvP files (Generate top.periph.jic and top.core.rbf) parameter in the Output Programming Files section.

Note: If you do not check this box, the Quartus Prime software does not create separate files for the periphery and core images.

- Click Save Conversion Setup to save these settings. For this exercise, call your settings cvp_base.cof. The Quartus Prime software does not automatically save your choices.

- Click Generate to create top.periph.jic and top.core.rbf.

Note: The generated CvP peripheral file size matches the size of the configuration device chosen.