3.2. Generating a 5G LPDC-V IP

To include the IP in a design, generate the IP in the Quartus® Prime software. Or optionally, you can generate a design example that includes the generated 5G LDPC-V IP, a C model, a MATLAB model, simulation scripts, and test data. The software generates no hardware example in Generate Example Design.

- Create a New Quartus® Prime project

- Open IP Catalog.

- Select DSP > Error Detection and Correction > 5G LDPC-V Intel FPGA IP and click Add

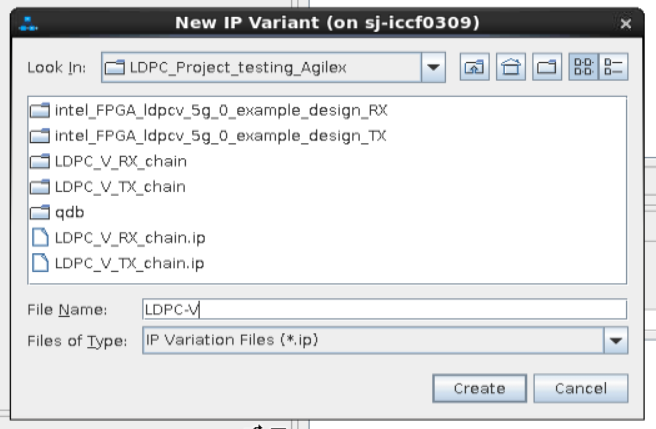

- Enter a name for your IP variant and click Create.

Figure 4. IP Variant File Name

The name is for both the top-level RTL module and the corresponding .ip file.The parameter editor for this IP appears.

The name is for both the top-level RTL module and the corresponding .ip file.The parameter editor for this IP appears. - Choose your parameters.

- For an optional design example, click Generate Example Design

No hardware example gets generated when you click Generate Example Design. If you upgrade the IP to a newer version, regenerate the example design.

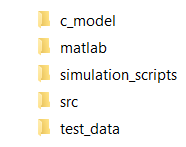

The software creates a design example of the transmitter or receiver. The software creates the target directory with files that you can use for MATLAB, C, or RTL simulations.Figure 5. Design Example Directory Structure

- Click Generate HDL.

Quartus® Prime generates the RTL and the files necessary to instantiate the IP in your design and synthesize it.