R-Tile Avalon® Streaming IP for PCI Express* Design Example User Guide

ID

683544

Date

10/28/2025

Public

1.2.1. Functional Description for the Programmed Input/Output (PIO) Design Example

1.2.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

1.2.3. Functional Description for the Performance Design Example

1.2.4. Functional Description for the Performance Design Example for TL Bypass Mode

1.2.5. Hardware and Software Requirements

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

2.3. Simulating the Design Example

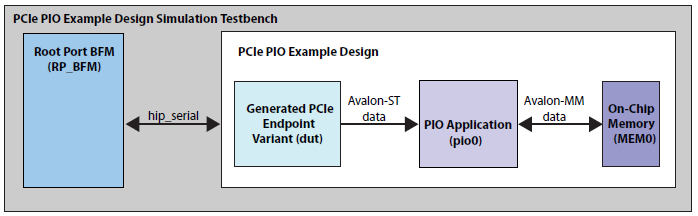

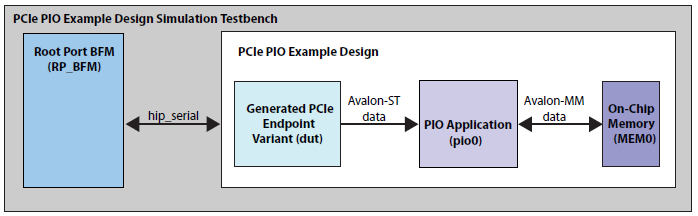

The simulation setup involves the use of a Root Port Bus Functional Model (BFM) to exercise the R-Tile Avalon® Streaming Intel FPGA IP for PCIe (DUT) as shown in the following figure.

Figure 22. PIO Design Example Simulation Testbench

Figure 23. SR-IOV Design Example Simulation Testbench

For a more detailed description of the testbench and the modules inside it, refer to Testbench. Also, for more details on the Root Port BFM specifically, refer to the Root Port BFM section.

The following flow diagram shows the steps to simulate the design example:

Figure 24. Procedure

The following figure shows the link status information for a Gen5 x16 Endpoint simulation:

Figure 25. Link Status for a Gen5 x16 Endpoint Simulation

After a successful simulation, the simulation.log file contains a "successful completion" message.

This testbench simulates up to a Gen5 x16 variant.