R-Tile Avalon® Streaming IP for PCI Express* Design Example User Guide

2.2.1. Generating the Design Example with R-Tile Configured in PIPE Mode

Simulation in PIPE mode (PHY Interface for the PCI Express) offers significant optimization in simulation times, as it allows for more direct and efficient communication between the simulation model and the physical layer.

PIPE mode simulation is supported for the PIO, SRIOV and Performance design examples. In the 25.1 release, PIPE mode simulation is supported for all simulators except Questa*-Altera® FPGA Edition.

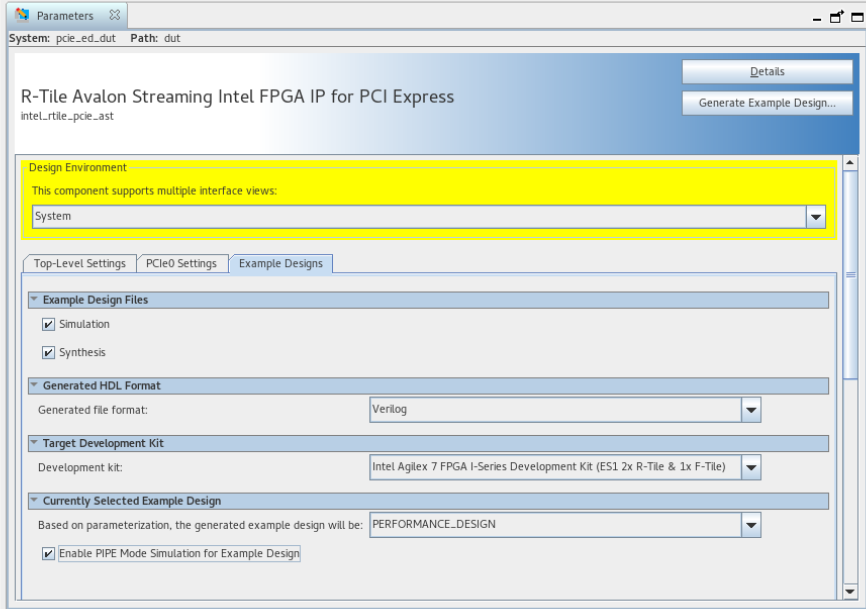

- On the Example Designs tab, verify that the Enable PIPE Mode Simulation for Example Design option is enabled by default.

The Enable PIPE Mode Simulation for Example Design option in the Example Designs tab of the IP Parameter Editor is enabled by default for PIPE mode when you generate the design example. If this option is turned off, the "+define+RTILE_PIPE_MODE" simulation option needs to be removed manually from the simulation command in the run_<simulator>* script before running it for Quartus® Prime Pro Edition v25.1.