1.5. Evaluation Period Timeout Indicator

The Intel® Quartus® Prime software installation includes the ocp_timeout_indicator IP block in the libraries\others\opercore_plus\ directory. You can instantiate this IP block in your design to alert when the device times out.

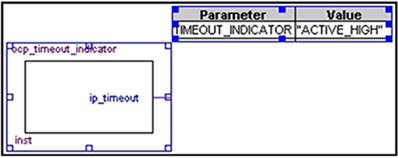

Specify either an active_high or active_low polarity of the time-out signal (ip_timeout) with the timeout_indicator parameter.

Figure 5. OCP_TIMEOUT_INDICATOR IP Block Symbol

Timeout Indicator VHDL Component Declaration

component ocp_timeout_indicator is

generic

(

TIMEOUT_INDICATOR: string := "ACTIVE_HIGH"

);

port

(

ip_timeout: out std_logic

);

end component ocp_timeout_indicator;Timeout Indicator VHDL Instantiation Prototype

My_Instance : ocp_timeout_indicator

GENERIC MAP(TIMEOUT_INDICATOR => "ACTIVE_HIGH")

PORT MAP(ip_timeout => My_Output);Timeout Indicator Verilog HDL Instantiation Prototype

ocp_timeout_indicator my_instance

(.ip_timeout(my_output));

defparam my_instance.TIMEOUT_INDICATOR =

"ACTIVE_HIGH";