AN 807: Configuring the Intel® Arria® 10 GX FPGA Development Kit for the Intel® FPGA SDK for OpenCL™

Troubleshooting

If you encounter errors when you configure the Intel® Arria® 10 GX FPGA Development Kit for the Intel® FPGA SDK for OpenCL™ , review the sections that follow for possible solutions.

The Quartus Programmer might display errors when your run aocl flash or aocl program

Info: Command: quartus_pgm -c 1 flash.cdf

Info (213045): Using programming cable "USB-BlasterII [2-1.1]"

Info (209060): Started Programmer operation at Wed Mar 22 13:56:27 2017

Error (209025): Can't recognize silicon ID for device 2

Error (209025): Can't recognize silicon ID for device 2

Error (209012): Operation failed

Info (209061): Ended Programmer operation at Wed Mar 22 13:56:28 2017

This error indicates that the MAX V CPLD system controller is not programmed with the correct image.

Solution

Use the Quartus Programmer to update the MAX V configuration with the max5_150.pof file for Intel® Arria® 10 GX FPGA Development Kit boards. If the error persists, program the FPGA with the top.sof file and program the flash memory with the aocl flash command again.

Quartus Programmer fails while programming either the FPGA or flash memory

- Error (209014): CONF_DONE pin failed to go high in device 1

- Error (209012): Operation failed

Solution

jtagconfig --setparam 1 JtagClock 6Mjtagconfig --getparam 1 JtagClockFor Microsoft* Windows users, Intel FPGA Download Cable driver might not be installed on your host

On Windows host systems, the Intel® FPGA Download Cable (formerly USB-Blaster) needs a driver installed for the cable to function properly.

Solution

Download the Intel® FPGA Download Cable driver from the Intel® FPGA Cable and Adapter Drivers Information page at the following URL:

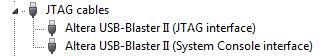

After you install the drivers, you should see the cable listed in Windows device manager as follows:

PCIe read/write speed is slower than expected

If you find that your PCIe read/write speed is slower than you expect, then your board might not be plugged into the correct PCIe slot.

Solution

Verify that your Intel® Arria® 10 GX FPGA Development Kit is plugged into the PCIe Gen3x8 slot on your host system. See " Configuring and Installing the Intel Arria 10 GX FPGA Development Kit board " to see what the correct PCIe slot looks like.

Memory module is not plugged in or a loose connection on the board

aocl diagnose: Running diagnose from

aocl diagnose: failed 32 times. First error below:

Vendor: Intel Corporation

MMD INFO: [acla10_ref0] uniphy(s) did not calibrate. Expected 0 but read 2

MMD INFO: If there are more failures than Uniphy controllers connected,

MMD INFO: ensure the uniphy_status core is correctly parameterized.

Solution

Confirm that you have connected the memory board, the power cable, and USB cable correctly as shown in " Configuring and Installing the Intel Arria 10 GX FPGA Development Kit board ". If you have confirmed your connections and continue to get this error, the memory board might not be seated correctly in the HiLo connector.

The jtagconfig command fails when initializing the Intel Arria 10 GX FPGA Development Kit for use with OpenCL

You might receive No JTAG hardware available error message when you run the jtagconfig command to lower the JTAG clock speed.

Solution

- Restart the jtag daemon using the following commands:

$ sudo killall -9 jtagd $ sudo jtagd - Confirm that the jtagconfig command works correctly. For example:

$jtagconfig 1) USB-BlasterII [3-11] 02E660DD 10AX115H1(.|E2|ES)/10AX115H2/.. 020A40DD 5M(1270ZF324|2210Z)/EPM2210

Unexpected reboot during programming the FPGA

You might experience an unexpected reboot during programming the FPGA on your Intel® Arria® 10 GX FPGA Development Kit leading to the FPGA not getting programmed and you are unable to proceed.

Solution

Program the non-volatile flash device manually using the following steps:

- Run the following commands to generate the flash.cof and flash.cdf files:

$ cd /hld $ source init_opencl.sh $ cd board/a10_ref/bringup $ aocl flash acl0Note: The aocl flash acl0 command above might report failed but it still generates the required flash.cof and flash.cdf files. - Verify that the flash.cof and flash.cdf are now in the bringup directory.

- Run the following commands to generate the flash.pof file and program the flash device:

$ jtagconfig --setparam 1 JtagClock 6M $ aocl binedit boardtest.aocx get .acl.fpga.bin fpga.bin $ aocl binedit fpga.bin get .acl.sof fpga_temp.sof $ quartus_cpf --convert flash.cof $ quartus_pgm -c 1 flash.cdf - Reboot the computer.

- Verify that the flash device was programmed correctly using the following steps:

- Run the following commands to install the driver:

$ cd /hld $ source init_opencl.sh $ aocl install /hld/board/a10_ref/ - Reboot the computer.

- Run the following commands to run the diagnostic:

$ cd /hld $ source init_opencl.sh $ aocl diagnose acl0One of the following might happen:

- If the aocl diagnose command passes, then the flash device was programmed correctly and you can proceed.

- If the aocl diagnose command fails, use the lspci command to verify that the card was recognized. Search for Intel® FPGA boards.

- If the lspci command displays that the board is recognized but the aocl diagnose command fails, then rerun the aocl install command.

- If the lspci command does not show that the board is recognized, double-check all switches and jumpers on the board and double-check that the memory module is seated correctly.

- Run the following commands to install the driver:

The aocl install command fails due to a problem with PCIe* drivers

The aocl install command might fail in Ubuntu* 16.04, kernel 4.14 or newer version because of a problem with the installed PCIe* drivers.

The following error message might appear after running the aocl install command:

Makefile:976: "Cannot use CONFIG_STACK_VALIDATION=y, please install libelf-dev,

libelf-devel or elfutils-libelf-devel"

Solution

To fix this issue, perform the following steps:

- Prevent the altera-cvp driver from being used in future by creating a text file /etc/modprobe.d/blacklist-altera-cvp.conf with a line blacklist altera_cvp.

- Rerun the aocl install command and verify that the error message does not appear.