3.3. 5G LDPC Simulation Results

Encoder Simulation Results

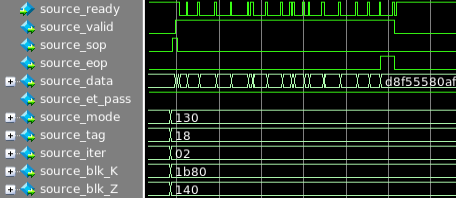

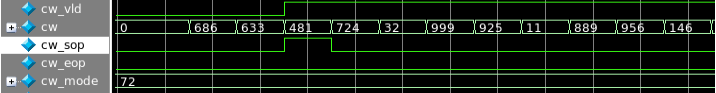

Figure 6. Input Message to the Encoder

| msg_mode | msg_vld | msg | msg_sop | msg_eop |

|---|---|---|---|---|

| 72 | HIGH | 686 | HIGH | LOW |

| 72 | HIGH | 633 | LOW | LOW |

| 72 | HIGH | 481 | LOW | LOW |

| 72 | HIGH | 724 | LOW | LOW |

| 72 | HIGH | 32 | LOW | LOW |

| 72 | HIGH | 999 | LOW | LOW |

| 72 | HIGH | 925 | LOW | LOW |

| 72 | HIGH | 11 | LOW | LOW |

| 72 | HIGH | 899 | LOW | LOW |

| 72 | HIGH | 956 | LOW | LOW |

| 72 | HIGH | 146 | LOW | LOW |

| 72 | HIGH | 463 | LOW | LOW |

| 72 | HIGH | 382 | LOW | LOW |

| 72 | HIGH | 447 | LOW | LOW |

| 72 | HIGH | 623 | LOW | LOW |

| 72 | HIGH | 285 | LOW | LOW |

| 72 | HIGH | 474 | LOW | LOW |

| 72 | HIGH | 102 | LOW | LOW |

| 72 | HIGH | 126 | LOW | LOW |

| 72 | HIGH | 951 | LOW | LOW |

| 72 | HIGH | 107 | LOW | LOW |

| 72 | HIGH | 237 | LOW | HIGH |

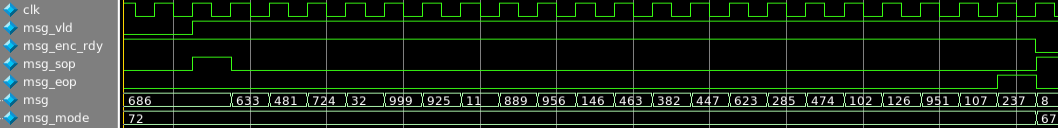

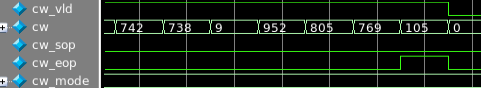

Figure 7. Data and Control Signals at the Start of the Encoder Codeword Output

| cw_vld | cw_mode | cw | cw_sop | cw_eop |

|---|---|---|---|---|

| LOW | 72 | 686 | LOW | LOW |

| LOW | 72 | 633 | LOW | LOW |

| HIGH | 72 | 481 | HIGH | LOW |

| HIGH | 72 | 724 | LOW | LOW |

| HIGH | 72 | 32 | LOW | LOW |

| HIGH | 72 | 999 | LOW | LOW |

| HIGH | 72 | 925 | LOW | LOW |

| HIGH | 72 | 11 | LOW | LOW |

| HIGH | 72 | 899 | LOW | LOW |

| HIGH | 72 | 956 | LOW | LOW |

| HIGH | 72 | 146 | LOW | LOW |

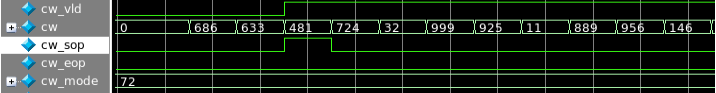

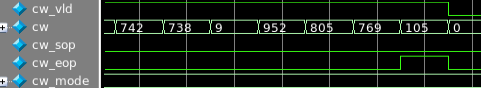

Figure 8. End of the Encoder Codeword Output

| cw_vld | cw_mode | cw | parity bits | cw_sop | cw_eop |

|---|---|---|---|---|---|

| HIGH | 72 | 742 | parity | LOW | LOW |

| HIGH | 72 | 738 | Parity | LOW | LOW |

| HIGH | 72 | 9 | parity | LOW | LOW |

| HIGH | 72 | 952 | parity | LOW | LOW |

| HIGH | 72 | 805 | parity | LOW | LOW |

| HIGH | 72 | 769 | parity | LOW | LOW |

| HIGH | 72 | 105 | parity | LOW | HIGH |

| LOW | Don’t care | Don’t care | Don’t care | LOW | LOW |

Decoder Simulation Results

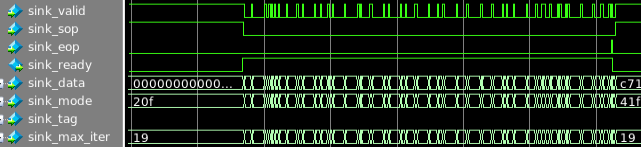

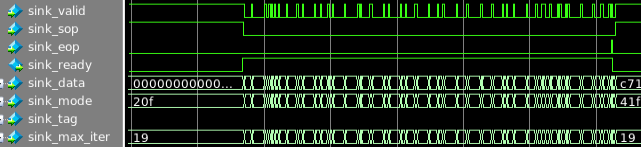

Figure 9. Codeword LLR Array Input to the Decoder

- sink_valid remains asserted for the duration of the LLR codeword while input data is valid. The upstream component can deassert it as needed.

- sink_sop is asserted only for the first data block in. It gets stretched for more than one clock cycle by the backpressure from the decoder, because the decoder deasserts sink_ready

- sink_eop pulses high for one clock cycle on the last valid input data block. It also can be stretched by the backpressure from the decoder’s sink.

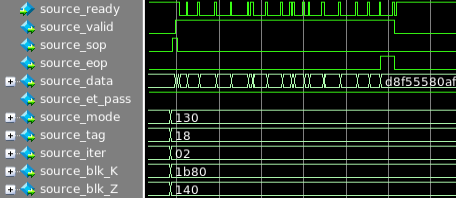

Figure 10. Decoded Message Output from the Decoder

- source_valid and source_sop are asserted about the same time. source_sop is asserted only for the first message block out

- The decoder may assert source_sop earlier and keep it high for a number of clock cycles – only the data block output during the last clock cycle just before source_sop is deasserted (and with source_valid asserted) is the actual beginning of the message

- source_valid remains asserted for the duration of the output message

- source_sop may get stretched for more than one clock cycle by the backpressure from the testbench, i.e. because the testbench deasserts source_ready downstream

- sink_eop is asserted for the last valid message block output. It also can be stretched by the backpressure from the sink downstream.