AN 736: Nios II Processor Booting From Altera Serial Flash (EPCQ)

ID

683104

Date

5/20/2016

Public

1.1. Definitions

1.2. Description of the Altera Serial Flash Controller

1.3. Scenarios for Booting Nios II from EPCQ Flash

1.4. Nios II Processor Configuration and Boot Flow

1.5. Steps to Build a Bootable System

1.6. EPCQ HAL Driver

1.7. Nios II Processor Booting Elements

1.8. Revision History for Nios II Booting From Altera Serial Flash (EPCQ)

1.5.1. Design

- Create your Nios® II processor project using Quartus II and Qsys.

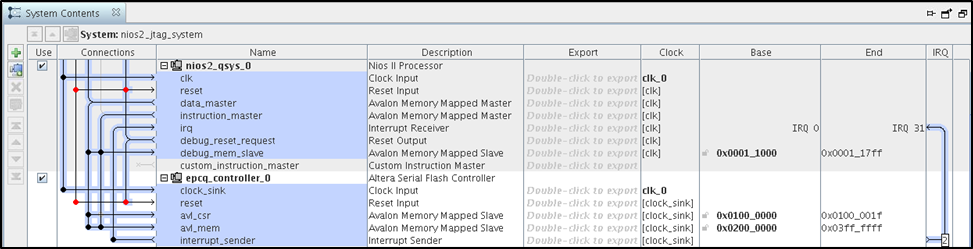

- Add the Intel® Serial Flash Controller IP to your Qsys system. Refer to the diagram below for the IP connection in Qsys.

Figure 3. Altera Serial Flash Controller IP Connections in Qsys

Note: The maximum input clock for Intel® Serial Flash Controller IP is 25 MHz. The input clock must not exceed this maximum value.

Note: The maximum input clock for Intel® Serial Flash Controller IP is 25 MHz. The input clock must not exceed this maximum value.