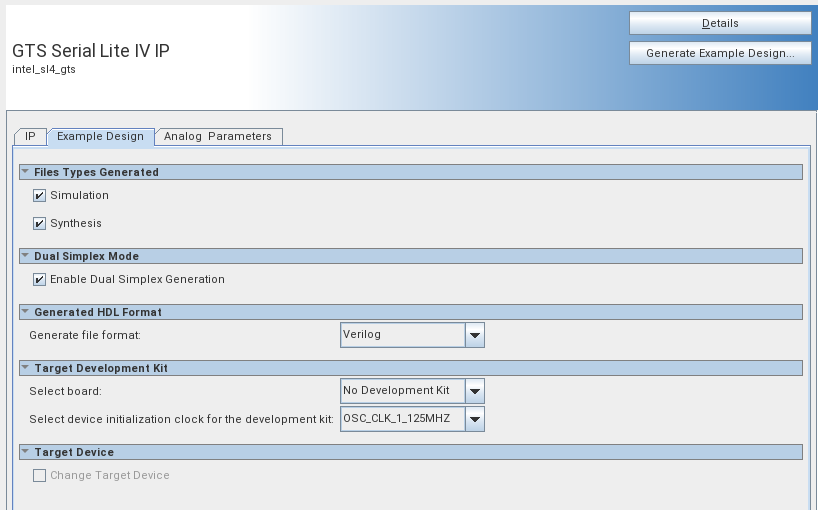

2.3.1. Design Example Parameters

| Parameter | Description |

|---|---|

| File Types Generated | The IP generates the necessary design example files for simulation and compilation. Simulation—select this option to generate the necessary design simulation files. Synthesis—select this option to generate the necessary design synthesis files. Use these files to compile the design in the Quartus® Prime Pro Edition software for hardware testing. |

| Dual Simplex Mode | Enable Dual Simplex Generation—enables Dual Simplex Example Design generation. This parameter is only available when PMA mode set as Tx/Rx. When this parameter is not available, the generated example design is duplex. When this parameter is available but not enabled, the generated example design is true simplex, where on the same transceiver channel(s) only simplex TX or simplex RX is placed. When this parameter is available and enabled, the generated example design is dual simplex, where both simplex TX IP and simplex RX IP are placed on the same transceiver channel(s). |

| Generate file format | The format of the RTL files for simulation—Verilog or VHDL. |

| Select Board | Supported hardware for design implementation. When you select an Intel FPGA development board, the Target Device is the one that matches the device on the Development Kit. If this menu is grayed out, there is no supported board for the options that you select. Agilex™ 5 FPGA E-Series 065B Premium Development Kit: This option allows you to test the design example on the selected Agilex™ 5 FPGA E-Series 065B Premium Development Kit.

Note: This option is only available when your target device is:

No Development Kit: This option excludes the hardware aspects for the design example. |

| Select device initialization clock for the development kit | This option provides support for the device initialization clock setting in the Example Design. The development kit only supports OSC_CLK_1_125MHZ by default. If you are using a different development kit board, please refer to the specifications of the board and set this setting manually in the project's QSF file. |

| Change Target Device | Select a different device grade for Intel® FPGA IP development kit. For device-specific details, refer to the device datasheet on the Intel FPGA website. |