Triple-Speed Ethernet IP Design Example User Guide: Agilex™ 3 and Agilex™ 5 FPGAs and SoCs

ID

813899

Date

10/24/2025

Public

1. 10/100/1000 Ethernet MAC Design Example with 1000BASE-X/SGMII 2XTBI PCS with GTS Transceiver

2. 10/100/1000 Multiport Ethernet MAC Design Example with 1000BASE-X/SGMII PCS and Embedded PMA (LVDS)

3. 10/100/1000 Ethernet MAC without Internal FIFO Buffers with 1000BASE-X/SGMII 2XTBI PCS and Embedded PMA Signals (GTS) with IEEE 1588v2

4. 10/100/1000 Ethernet MAC without Internal FIFO Buffers with 1000BASE-X/SGMII TBI PCS and Embedded PMA Signals (LVDS I/O) with IEEE 1588v2

5. Triple-Speed Ethernet IP Design Example User Guide: Agilex™ 3 and Agilex™ 5 FPGAs and SoCs Archives

6. Document Revision History for the Triple-Speed Ethernet IP Design Example User Guide: Agilex™ 3 and Agilex™ 5 FPGAs and SoCs

1.2.5.1. Test Procedure

After you compile the Triple-Speed Ethernet IP design example and configure it on your Agilex™ 3 and Agilex™ 5 device, you can use the System Console to program the IP.

To turn on the System Console and test the hardware design example, follow these steps:

- In the Quartus® Prime Pro Edition software, select Tools > System Debugging Tools>System Console to launch the system console.

- In the Tcl Console pane, type cd hwtest/agx/2xtbi_pma to change directory to <design_example_dir>/hardware_test_design/hwtest/agx/2xtbi_pma.

- Type source basic/basic.tcl.

- Type list_jtag to display a list of JTAG master indexes that are connected to your board.

- Type set_jtag<number_of appropriate_JTAG_master> to select the JTAG master.

- For hardware testing:

To perform external loopback testing, type source hwtest_main.tcl to run the design example in 10Mbps, 100 Mbps, and 1Gbps ethernet speed.

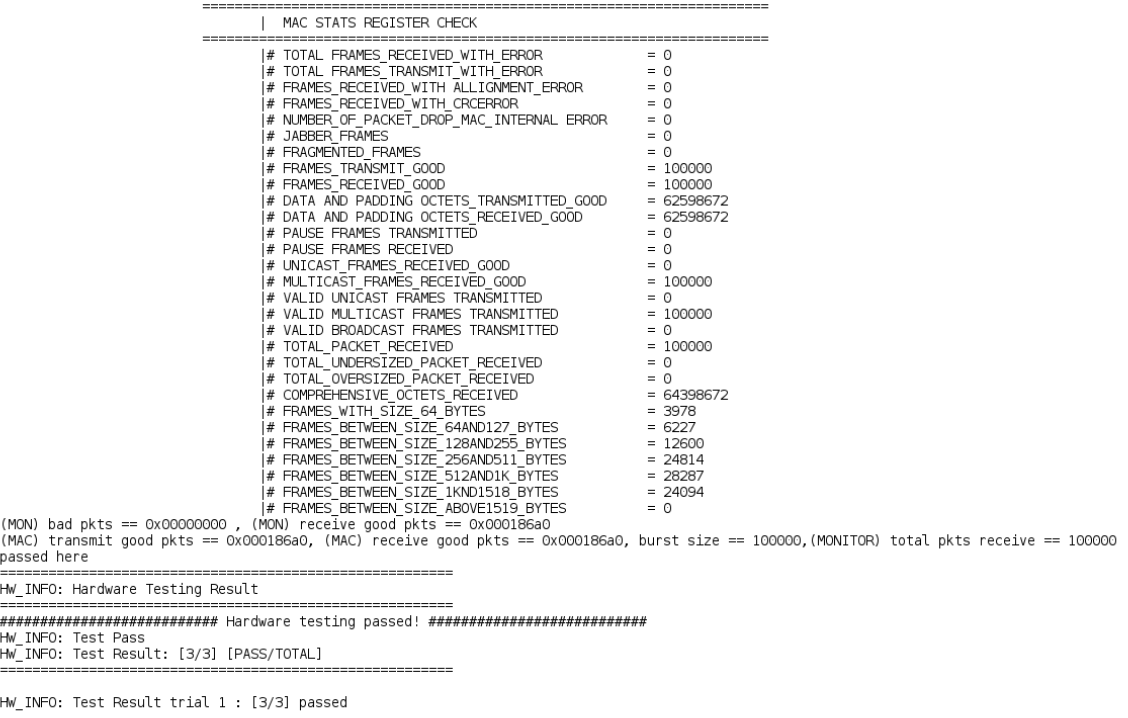

Results: A successful test run displays the following message:

To perform serial internal loopback testing, type source hwtest_main_silb.tcl to run the design example in 10Mbps, 100 Mbps, and 1Gbps ethernet speed to run serial internal loopback test.

Results: A successful test displays the following message:

% source hwtest_main_silb.tcl HW_INFO: Starting Internal Loopback Testing ISSP Reset Applied ISSP Reset released ------------------------------------------------------ Asserting Reset ------------------------------------------------------ ====================================================== ENABLING SILB ====================================================== 1. 0xF9A30F 2. 0x00f9a30f Polling successfull Bit 15: 0x000001 , Bit 14: 0x000000 1. 0xF9230F 2. 0x00f9230f Polling successfull Bit 15: 0x000000 , Bit 14: 0x000000 1. 0x00A303 2. 0x0000a303 Polling successfull Bit 15: 0x000001 , Bit 14: 0x000000 1. 0x002303 2. 0x00002303 Polling successfull Bit 15: 0x000000 , Bit 14: 0x000000 1. 0x6A340 2. 0x0006a340 Polling successfull Bit 15: 0x000001 , Bit 14: 0x000000 1. 0x62340 2. 0x00062340 Polling successfull Bit 15: 0x000000 , Bit 14: 0x000000 ------------------------------------------------------ Releasing Reset ------------------------------------------------------ Value from issp reset probe is 0x3/0b11 Rx Lane status is : 1 Rx Lane reset status is 1 ###################################################### Value from issp reset probe is 0x3/0b11 Serial loopback on Lane# 3 is enabled ###################################################### HW_INFO: Testing TEST_SMA_LB 1G CONFIGURE CHANNEL 0 TSE_MAC_BASE_ADDR is 131072 TSE_PHY_BASE_ADDR is 131584 Start:Config 1 port... Step 1: Config PCS ! Config SGMIIPCS... Setting up PCS with a basic working config Start: Set PCS SGMII PCS ENA End. Enable SGMII mode... Disable PCS Auto-Negotiation Disable AN... speed is = 0x00000001 1G IF_MODE after set speed = 0x00000009(MON) bad pkts == 0x00000000 , (MON) receive good pkts == 0x000186a0 (MAC) transmit good pkts == 0x000186a0, (MAC) receive good pkts == 0x000186a0, burst size == 100000, (MONITOR) total passed here ======================================================= HW_INFO: Hardware Testing Result ======================================================= ############# Hardware testing passed! ################ HW_INFO: Test Pass HW_INFO: Test Result: [3/3][PASS/TOTAL] ======================================================= HW_INFO: Test Result trial 1:[3/3] passed ------------------------------------------------------- Asserting Reset ------------------------------------------------------- ======================================================= DISABLING SILB ====================================================== 1. 0xF9A30F 2. 0x00f9a30f Polling successfull Bit 15: 0x000001 , Bit 14: 0x000000 1. 0xF9230F 2. 0x00f9230f Polling successfull Bit 15: 0x000000 , Bit 14: 0x000000 1. 0x00A303 2. 0x0000a303 Polling successfull Bit 15: 0x000001 , Bit 14: 0x000000 1. 0x002303 2. 0x00002303 Polling successfull Bit 15: 0x000000 , Bit 14: 0x000000 1. 0x0A340 2. 0x0000a340 Polling successfull Bit 15: 0x000001 , Bit 14: 0x000000 1. 0x02340 2. 0x00002340 Polling successfull Bit 15: 0x000000 , Bit 14: 0x000000 Releasing Reset Value from issp reset probe is 0x3/0b11 Serial loopback on Lane#3 is disabled

Note: For the test procedure of serial internal loopback, refer to GTS Attribute Access Method in the GTS Transceiver PHY User Guide: Agilex™ 5 FPGAs and SoCs.

Related Information