A newer version of this document is available. Customers should click here to go to the newest version.

6.1. Synthesis Tool

6.2. Device Resource Reports

6.3. Quartus® Prime Message

6.4. Design Assistant Design Rule Checking

6.5. Timing Constraints and Analysis

6.6. Area and Timing Optimization

6.7. Preserving Performance and Reducing Compilation Time

6.8. Designing with Hyperflex®

6.9. Simulation

6.10. Power Analysis

6.11. Design Implementation, Analysis, Optimization and Verification Revision History

4.1.1.1. Partial Reconfiguration

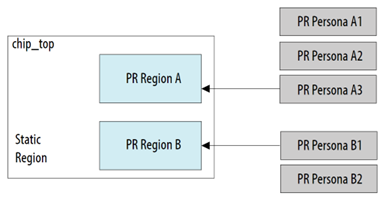

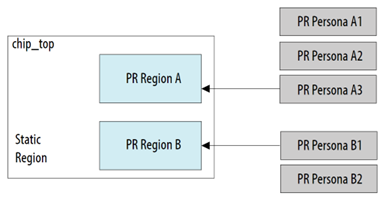

Partial reconfiguration (PR) is supported for Agilex™ 5 . PR allows you to reconfigure a portion of the FPGA dynamically, while the remaining FPGA design continues to function. You can define multiple personas for a particular region in your design, without impacting operation in areas outside this region. This methodology is effective in systems with multiple functions that time-share the same FPGA device resources. PR enables the implementation of more complex FPGA systems.

Figure 2. Partial Reconfiguration Multiple Personas

For more information about partial reconfiguration, refer to Quartus® Prime Pro Edition User Guide: Partial Reconfiguration.

Related Information