External Memory Interfaces Agilex™ 7 M-Series FPGA IP Design Example User Guide

ID

772632

Date

7/07/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the External Memory Interfaces Agilex™ 7 M-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

4. Document Revision History for External Memory Interfaces Agilex™ 7 M-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Parameterizing the External Memory Interface for HPS IP

2.4. Configuring DQ Pin Swizzling

2.5. Generating the Synthesizable EMIF Design Example

2.6. Back Annotating Pin Placement and I/O Standard Assignments

2.7. Generating the EMIF Design Example for Simulation

2.8. Pin Placement for Agilex™ 7 M-Series EMIF IP

2.9. Compiling the Agilex™ 7 M-Series EMIF Design Example

2.10. Using the EMIF Design Example with the Test Engine IP

2.11. Generating the EMIF Design Example with the Performance Monitor

2.4.1. Example: DQ Pin Swizzling Within DQS group for x32 DDR4 interface

2.4.2. Example: Byte Swizzling for a x32 DDR4 interface, using a memory device of x8 width

2.4.3. Combining Pin and Byte Swizzling

2.4.4. Example: Swizzling for a x32 + ECC interface

2.4.5. Example: Swizzling for a 2Ch x32 + ECC interface

2.4.6. Example: Byte Swizzling for Lockstep Configuration

2.10. Using the EMIF Design Example with the Test Engine IP

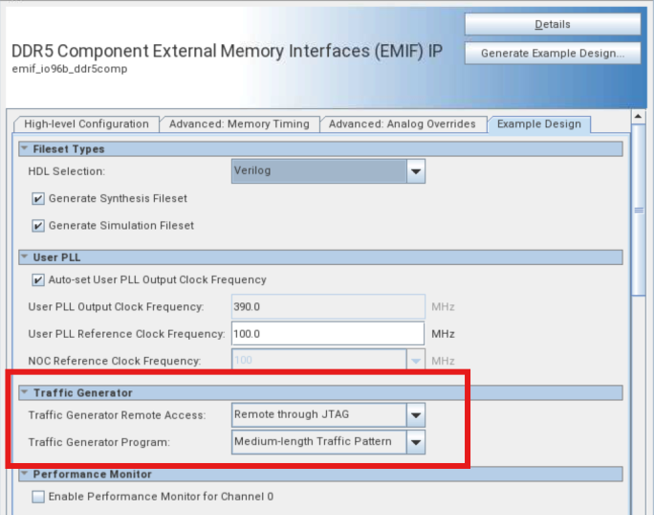

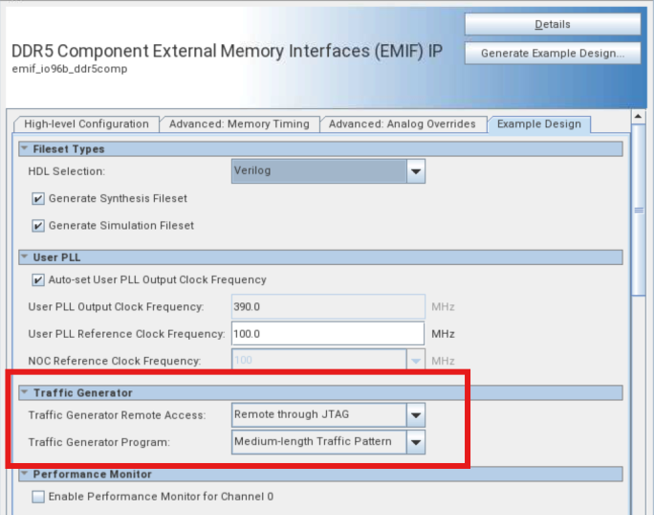

The test engine IP is a software-programmable AXI traffic generator that generates a configurable pattern of reads and writes to a programmable memory address range. You can modify the length of the default traffic on the Design Example tab.

Figure 31. Using the Test Engine IP

Follow these steps to use the EMIF Design Example with the Test Engine IP.

- Change directory to the location where the .bin folder resides. (By default, this is the /qii folder.)

At the command line, type the following:

system-console --script=<path to testengine_library.tcl> --sof=<path to sof_file> --update=1 --n-loops=1

Example:

system-console --script=hydra_sw/testengine_library.tcl --sof=ed_synth.sof --update=1 --n-loops=1

This example reprograms the driver with the traffic pattern in the .bin folder, and runs the traffic test for 1 loop. If you do not want to reprogram the driver, change --update=1 to --update=0.

The main advantage of the new test engine IP is that you don't need to recompile your entire design when you change or modify the traffic pattern. You need only regenerate the test engine pattern binary files. For additional information on test engine IP functions, refer to the testengine_library.tcl file.