F-Tile Dynamic Reconfiguration Design Example User Guide

ID

710582

Date

12/19/2022

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. Quick Start Guide

2. Detailed Description for CPRI Multirate Design Example

3. Detailed Description for PMA/FEC Direct PHY Multirate Design Example

4. Detailed Description for Ethernet Multirate Design Example

5. Detailed Description for Ethernet to CPRI Design Example

6. F-Tile Dynamic Reconfiguration Design Example User Guide Archives

7. Document Revision History for F-Tile Dynamic Reconfiguration Design Example User Guide

1.2.1. CPRI Multirate Design Example Parameters

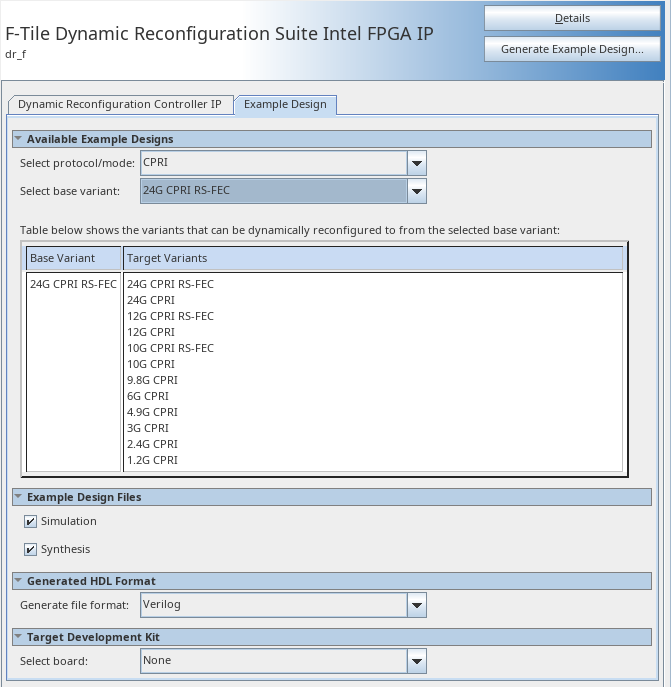

Figure 3. CPRI Multirate Example Design Tab

| Parameters | Value | Description |

|---|---|---|

| Select Protocol/mode | CPRI | Select the IP protocol for dynamic reconfiguration. |

| Select Base Variant | 24G CPRI RS-FEC | Select the configuration of base variant for dynamic reconfiguration. |

| Example Design Files | Simulation Synthesis |

Simulation option generates the testbench and compilation-only project. Synthesis option generates the hardware design example. |

| Generated File Format | Verilog VHDL |

Select the HDL files format. If you select VHDL, you must simulate the testbench with a mixed-language simulator. |

| Target Development Kit | None Agilex I-Series Transceiver-SoC Development Kit |

Specify the target device for the hardware example design. This option is only available if you select the Synthesis option. |