AN 964: Signal Tap Tutorial for Intel Agilex® 7 Partial Reconfiguration Designs

ID

710463

Date

10/02/2023

Public

2.1. Step 1: Getting Started

2.2. Step 2: Preparing the Base Revision

2.3. Step 3: Preparing the Implementation Revisions for Debugging

2.4. Step 4: Configuring Signal Tap Logic Analyzer

2.5. Step 5: Generating Programming Files

2.6. Step 6: Programming the FPGA Device

2.7. Step 7: Performing Data Acquisition

2.4.2.1. Add Acquisition Clock

Specify the reference clock that Signal Tap uses during acquisition.

Perform the following steps in the Signal Configuration pane:

- Next to Clock, click … to open the Node Finder.

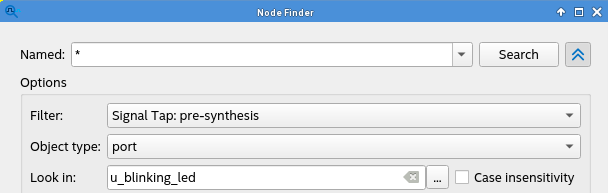

- Set the following search parameters:

Field Value Named * Look in top|u_blinking_led Figure 22. Search Parameters to Find the Clock

- Click Search.

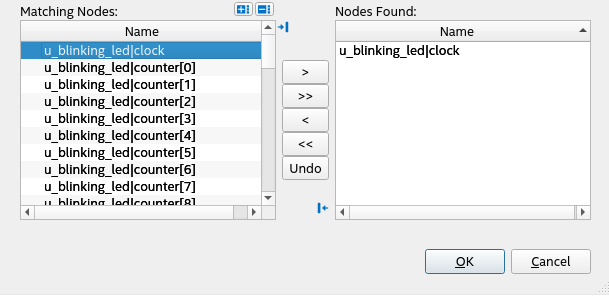

Figure 23. Select Clock in Node Finder

- Select clock, click >, and then click OK.