1. Before You Begin

2. Introduction

3. Functional Description

4. Interface Overview

5. Parameters (H-Tile)

6. Parameters (P-Tile) (F-Tile) (R-Tile)

7. Designing with the IP Core

8. Software Programming Model

9. Registers

10. Troubleshooting/Debugging

11. Multi Channel DMA FPGA IP for PCI Express User Guide Archives

12. Revision History for the Multi Channel DMA FPGA IP for PCI Express User Guide

3.1. Multi Channel DMA

3.2. Bursting Avalon-MM Master (BAM)

3.3. Bursting Avalon-MM Slave (BAS)

3.4. MSI Interrupt

3.5. Config Slave (CS)

3.6. Root Port Address Translation Table Enablement

3.7. Hard IP Reconfiguration Interface

3.8. Config TL Interface

3.9. Configuration Intercept Interface (EP Only)

3.10. Data Mover Only

4.1. Port List

4.2. Clocks

4.3. Resets

4.4. Multi Channel DMA

4.5. Bursting Avalon-MM Master (BAM) Interface

4.6. Bursting Avalon-MM Slave (BAS) Interface

4.7. Legacy Interrupt Interface

4.8. Hot Plug Interface (RP only)

4.9. MSI Interface

4.10. Config Slave Interface (RP only)

4.11. Hard IP Reconfiguration Interface

4.12. Config TL Interface

4.13. Configuration Intercept Interface (EP Only)

4.14. Data Mover Interface

4.15. Hard IP Status Interface

4.16. Precision Time Management (PTM) Interface

8.1.6.1. ifc_api_start

8.1.6.2. ifc_mcdma_port_by_name

8.1.6.3. ifc_qdma_device_get

8.1.6.4. ifc_num_channels_get

8.1.6.5. ifc_qdma_channel_get

8.1.6.6. ifc_qdma_acquire_channels

8.1.6.7. ifc_qdma_release_all_channels

8.1.6.8. ifc_qdma_device_put

8.1.6.9. ifc_qdma_channel_put

8.1.6.10. ifc_qdma_completion_poll

8.1.6.11. ifc_qdma_request_start

8.1.6.12. ifc_qdma_request_prepare

8.1.6.13. ifc_qdma_descq_queue_batch_load

8.1.6.14. ifc_qdma_request_submit

8.1.6.15. ifc_qdma_pio_read32

8.1.6.16. ifc_qdma_pio_write32

8.1.6.17. ifc_qdma_pio_read64

8.1.6.18. ifc_qdma_pio_write64

8.1.6.19. ifc_qdma_pio_read128

8.1.6.20. ifc_qdma_pio_write128

8.1.6.21. ifc_qdma_pio_read256

8.1.6.22. ifc_qdma_pio_write256

8.1.6.23. ifc_request_malloc

8.1.6.24. ifc_request_free

8.1.6.25. ifc_app_stop

8.1.6.26. ifc_qdma_poll_init

8.1.6.27. ifc_qdma_poll_add

8.1.6.28. ifc_qdma_poll_wait

8.1.6.29. ifc_mcdma_port_by_name

7.2. Simulating the IP Core

The Quartus® Prime Pro Edition software optionally generates a functional simulation model, a testbench or design example, and vendor-specific simulator setup scripts when you generate your parameterized Multi Channel DMA for PCI Express IP core. For Endpoints, the generation creates a Root Port BFM. There is no support for Root Ports in this release of the Quartus® Prime Pro Edition.

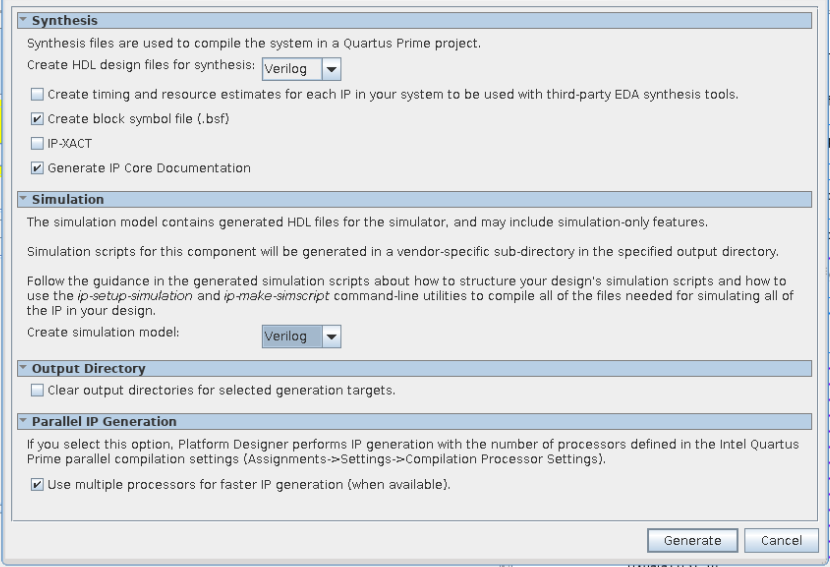

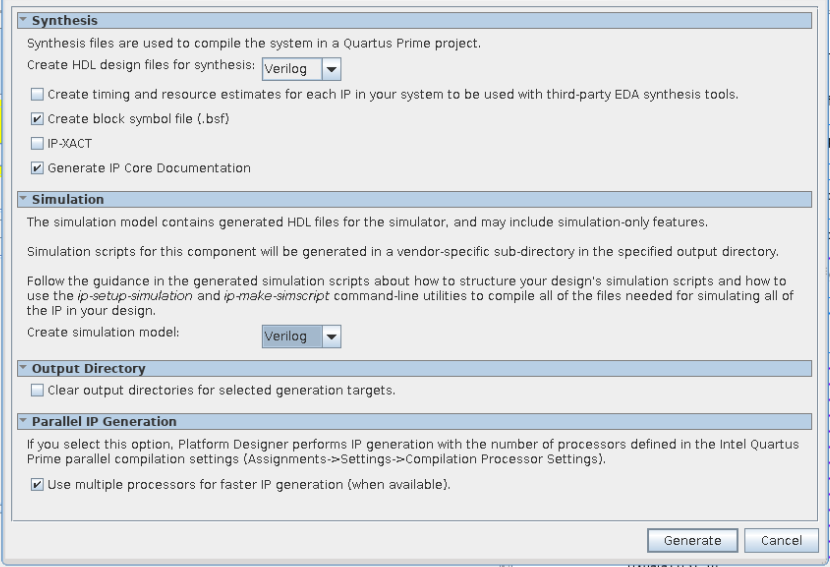

To enable IP simulation model generation, set Create simulation model to Verilog or VHDL when you generate HDL:

Figure 43. Multi Channel DMA IP for PCI Express Simulation in Quartus® Prime Pro Edition

For information about supported simulators, refer to the Multi Channel DMA for PCI Express Intel FPGA IP Design Example User Guide.

Note: Root Port simulation is supported by VCS only.

Note: The Intel testbench and Root Port BFM provide a simple method to do basic testing of the Application Layer logic that interfaces to the PCIe IP variation. This BFM allows you to create and run simple task stimuli with configurable parameters to exercise basic functionality of the example design. The testbench and Root Port BFM are not intended to be a substitute for a full verification environment. Corner cases and certain traffic profile stimuli are not covered. To ensure the best verification coverage possible, Intel strongly recommends that you obtain commercially available PCIe verification IP and tools, or do your own extensive hardware testing, or both.