A newer version of this document is available. Customers should click here to go to the newest version.

3.2. Generating a 5G LPDC-V IP

To include the IP in a design, generate the IP in the Intel® Quartus® Prime software. Or optionally, you can generate a design example that includes the generated 5G LDPC-V IP, a C model, a MATLAB model, simulation scripts, and test data. The software generates no hardware example in Generate Example Design.

- Create a New Intel® Quartus® Prime project

- Open IP Catalog.

- Select DSP > Error Detection and Correction > 5G LDPC-V and click Add

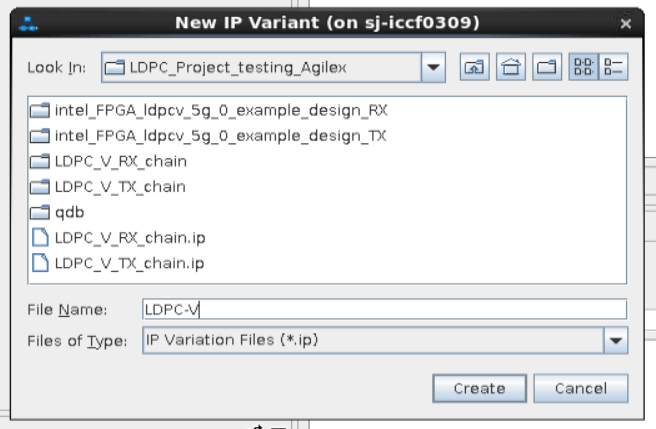

- Enter a name for your IP variant and click Create.

Figure 4. IP Variant File Name

The name is for both the top-level RTL module and the corresponding .ip file.The parameter editor for this IP appears.

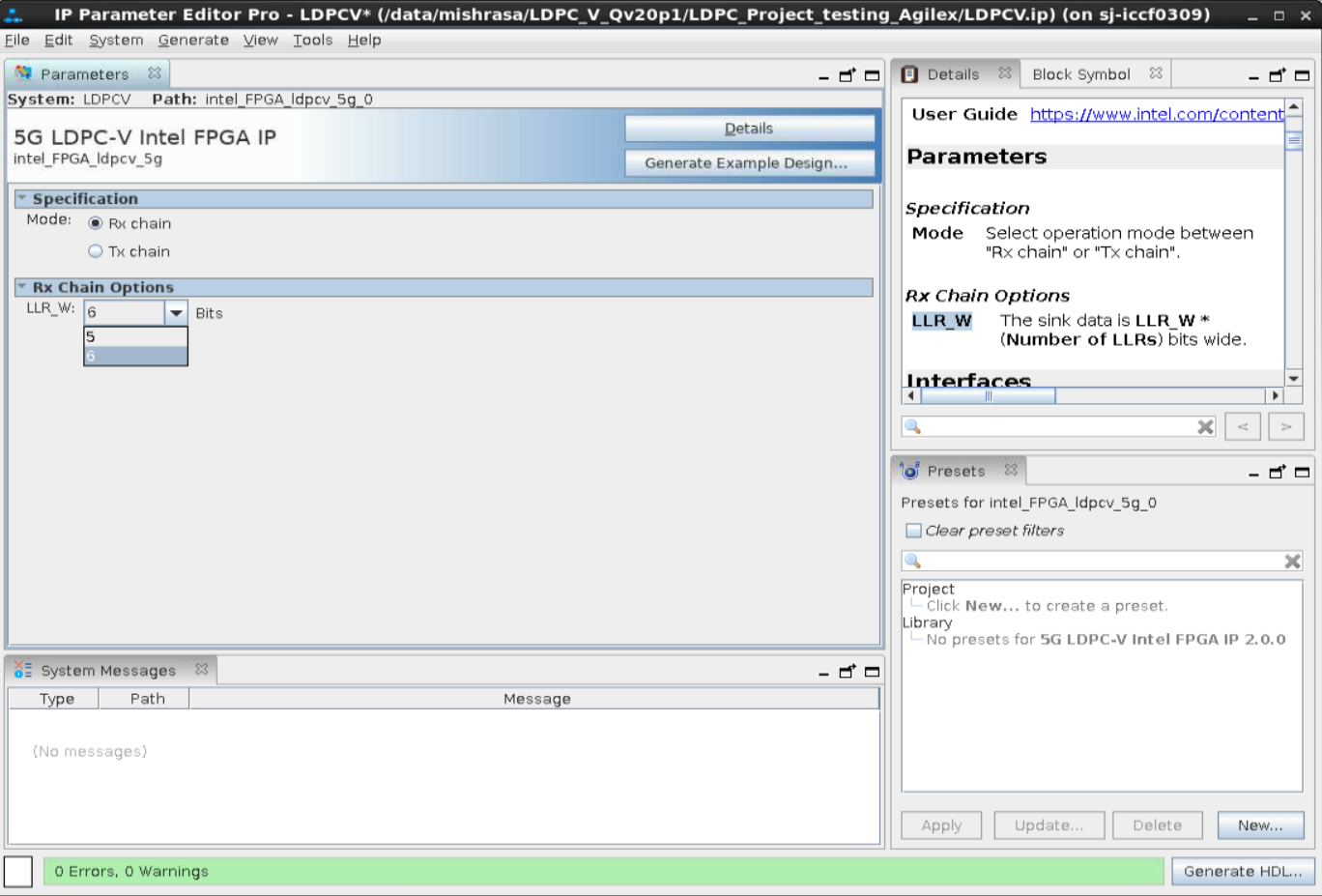

The name is for both the top-level RTL module and the corresponding .ip file.The parameter editor for this IP appears. - Choose your parameters.

Table 6. 5G LDPC-V Parameters Parameter Name Values Description Mode Rx chain

Tx chain

Select between receiver or transmitter. LLR_W (receiver only) 5

6

Input LLR bitwidth. LLR_W=5, gives 3 integral bits and 2 fractional bits, i.e. a range of [-4.0, 3.75]

LLR_W=6, gives 4 integral bits and 2 fractional bits, i.e. a range of [-8.0, 7.75]

NUM_DECODERS (receiver only)

1

2

The number of decoders that the IP builds. MAX_LF_DECODER1 (receiver only)

96

128

192

The maximum lifting factor for the packet that the second decoder can process. Only valid when NUM_DECODERS is to 2 Figure 5. 5G LDPC Parameter Editor

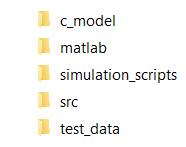

- For an optional design example, click Generate Example Design

The software creates a design example of the transmitter or receiver.Figure 6. Design Example Directory Structure

- Click Generate HDL.

Intel® Quartus® Prime generates the RTL and the files necessary to instantiate the IP in your design and synthesize it.

Related Information