L-Tile and H-Tile Avalon® Memory-mapped+ Intel® FPGA IP for PCI Express* User Guide

ID

683527

Date

9/13/2024

Public

1. Introduction

2. Quick Start Guide

3. Block and Interface Descriptions

4. Parameters

5. Designing with the IP Core

6. Registers

7. Design Example and Testbench

8. Document Revision History for Intel® L- and H-tile Avalon® Memory-mapped+ IP for PCI Express* User Guide

A. Avalon-MM IP Variants Comparison

B. Root Port BFM

C. BFM Procedures and Functions

D. Troubleshooting and Observing the Link Status

E. Root Port Enumeration

2.1. Design Components

2.2. Directory Structure

2.3. Generating the Design Example

2.4. Simulating the Design Example

2.5. Compiling the Design Example and Programming the Device

2.6. Installing the Linux Kernel Driver

2.7. Running the Design Example Application

2.8. Ensuring the Design Example Meets Timing Requirements

6.1.1. Register Access Definitions

6.1.2. PCI Configuration Header Registers

6.1.3. PCI Express Capability Structures

6.1.4. Intel Defined VSEC Capability Header

6.1.5. Uncorrectable Internal Error Status Register

6.1.6. Uncorrectable Internal Error Mask Register

6.1.7. Correctable Internal Error Status Register

6.1.8. Correctable Internal Error Mask Register

C.1. ebfm_barwr Procedure

C.2. ebfm_barwr_imm Procedure

C.3. ebfm_barrd_wait Procedure

C.4. ebfm_barrd_nowt Procedure

C.5. ebfm_cfgwr_imm_wait Procedure

C.6. ebfm_cfgwr_imm_nowt Procedure

C.7. ebfm_cfgrd_wait Procedure

C.8. ebfm_cfgrd_nowt Procedure

C.9. BFM Configuration Procedures

C.10. BFM Shared Memory Access Procedures

C.11. BFM Log and Message Procedures

C.12. Verilog HDL Formatting Functions

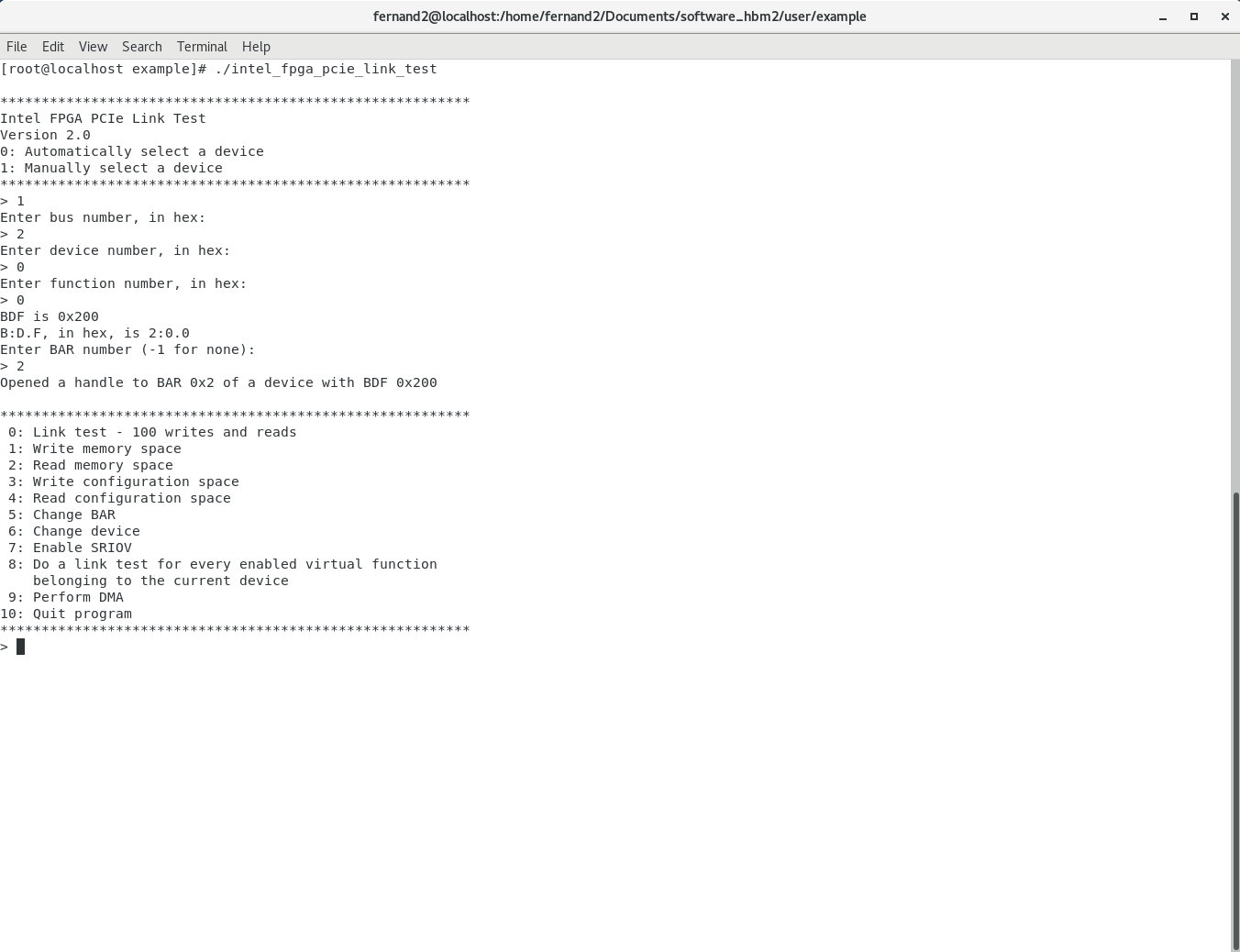

2.7. Running the Design Example Application

- Navigate to ./software/user/example under the design example directory.

- Compile the design example application:

$ make

- Run the test:

$ sudo ./intel_fpga_pcie_link_test

You can run the Intel® FPGA IP PCIe* link test in manual or automatic mode.

- In automatic mode, the application automatically selects the device. The test selects the Stratix® 10 PCIe* device with the lowest BDF by matching the Vendor ID. The test also selects the lowest available BAR.

- In manual mode, the test queries you for the bus, device, and function number and BAR.

For the Stratix® 10-GX Development Kit, you can determine the BDF by typing the following command:$ lspci -d 1172

- Here is a sample transcript for manual mode: