A newer version of this document is available. Customers should click here to go to the newest version.

2.3. Specifying the IP Core Parameters and Options

The IP parameter editor allows you to quickly configure your custom IP variation. Perform the following steps to specify IP core options and parameters in the Intel® Quartus® Prime Pro Edition software.

The Interlaken IP is not supported in Platform Designer. You must use the IP Catalog accessible from the Intel® Quartus® Prime Pro Edition Tools menu. The Interlaken IP does not support VHDL simulation models. You must specify the Verilog HDL for both synthesis and simulation models.

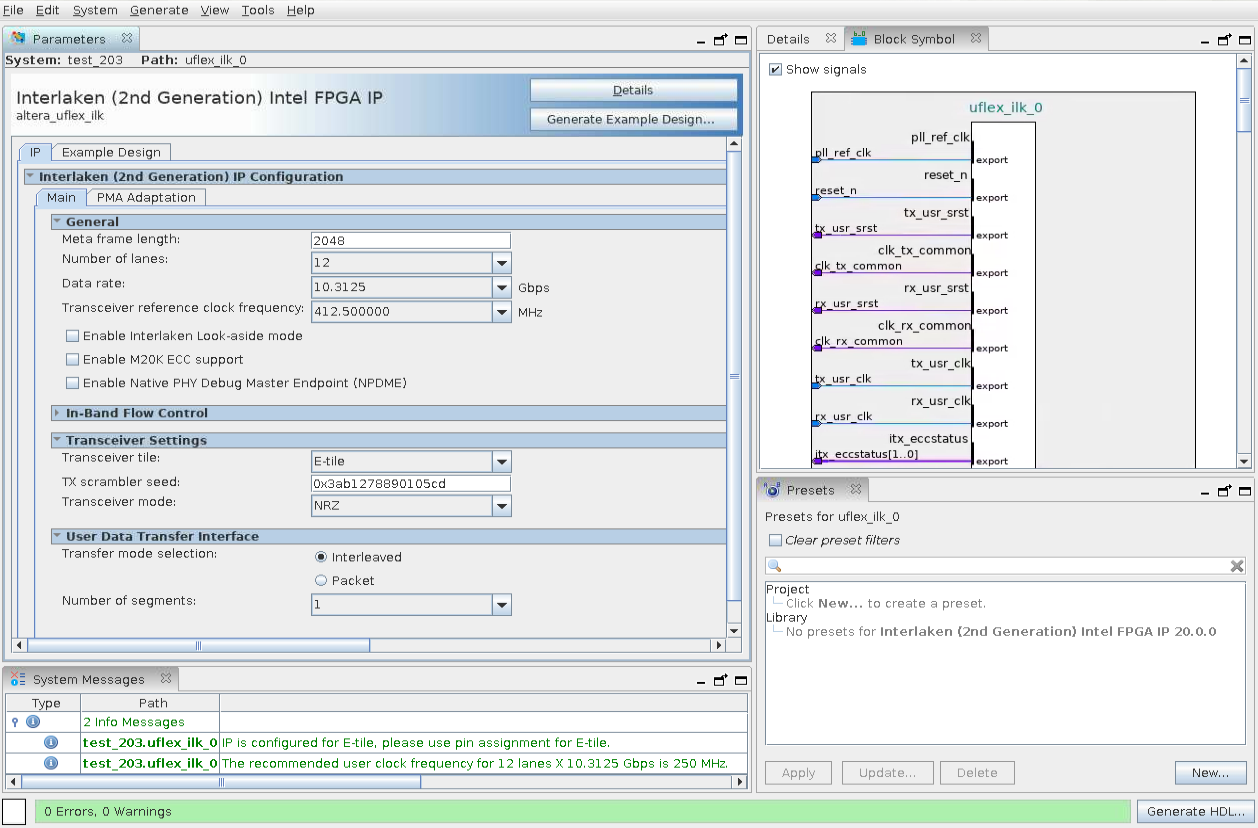

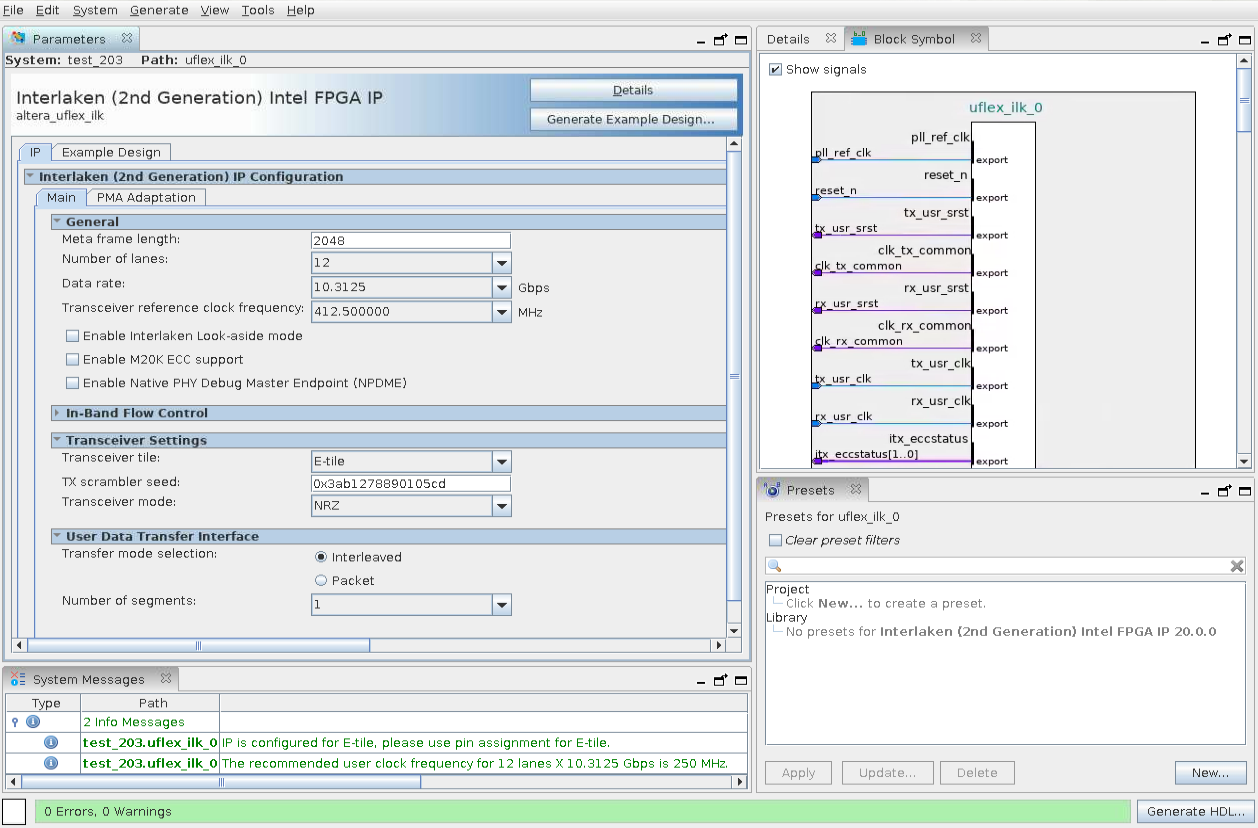

IP Parameter Editor

- In the Intel® Quartus® Prime Pro Edition software, click File > New Project Wizard to create a new Intel® Quartus® Prime project, or File > Open Project to open an existing Intel® Quartus® Prime project. The wizard prompts you to specify a device.

- Select the device family either Stratix 10 (GX/SX/MX/TX) or Intel Agilex® 7 (F-Series/M-Series/I-Series) as your target device.

- In the IP Catalog (Tools > IP Catalog), locate and double-click Interlaken (2nd Generation) Intel® FPGA IP . The New IP Variant window appears.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your_ip> .ip.

- Click Create. The parameter editor appears.

- On the IP tab, specify the parameters and options for your IP variation, including one or more of the following. Refer to Parameter Settings for information about specific IP core parameters.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

- Click Generate HDL. The Generation dialog box appears.

- Specify output file generation options, and then click Generate. The IP variation files generate according to your specifications.

- Optionally, click Generate Example Design tab in the parameter editor to generate a demonstration testbench and example design for your IP core variation.

- Click Finish. The parameter editor adds the top-level .ip file to the project automatically. If you are prompted to manually add the .ip file to the project, click Project > Add/Remove Files in Project to add the file.

- After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.