F-Tile Avalon® Streaming IP for PCI Express* Design Example User Guide

ID

683372

Date

10/20/2025

Public

3.8.3. Running the Performance Design Example

Note: The Performance Design Example hardware test is currently supported at 500 MHz only.

- Navigate to ./software/user/example under the design example directory.

- Compile the design example application:

$ make

-

Run the test:

$ sudo ./intel_fpga_pcie_link_test

You can run the FPGA IP PCIe link test application in manual or automatic mode. Select from:- In automatic mode, the application automatically selects the device. The test selects the Altera PCIe device with the lowest BDF by matching the Vendor ID. The test also selects the lowest available BAR.

- In manual mode, the test queries you for the bus, device, and function number and BAR.

For the Agilex™ 7 Development Kit, you can determine the BDF by typing the following command:$ sudo lspci -d 1172:

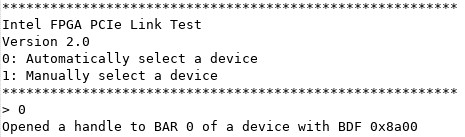

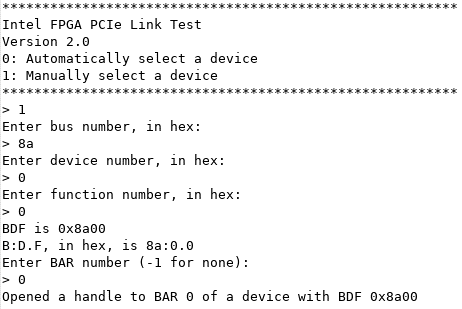

- Here are sample transcripts for automatic and manual modes:

Figure 32. Automatic Mode

Figure 33. Manual Mode

Figure 33. Manual Mode

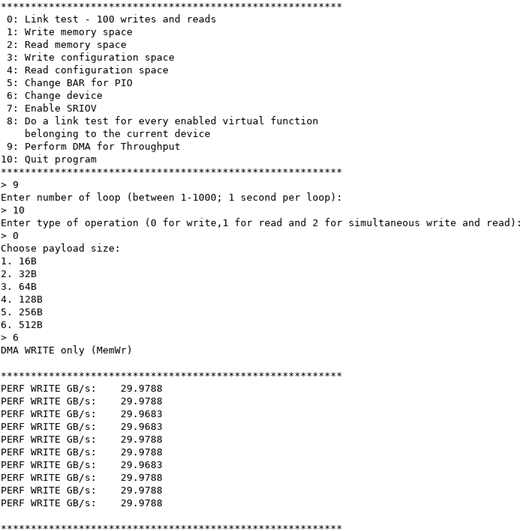

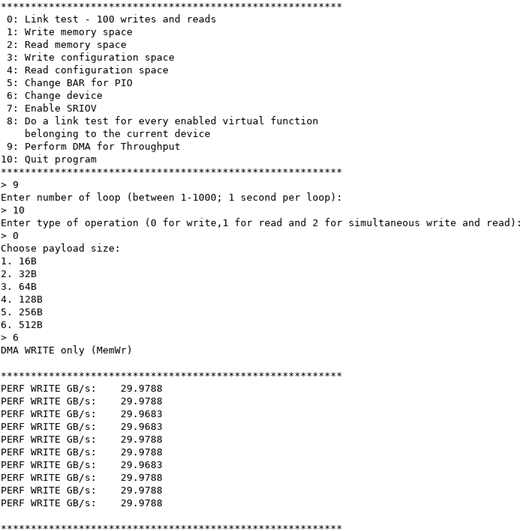

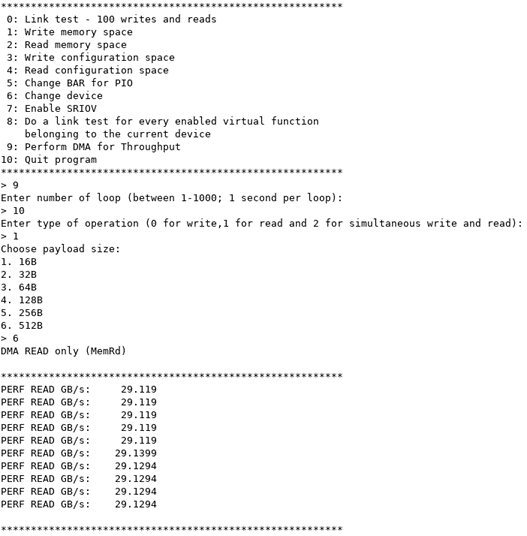

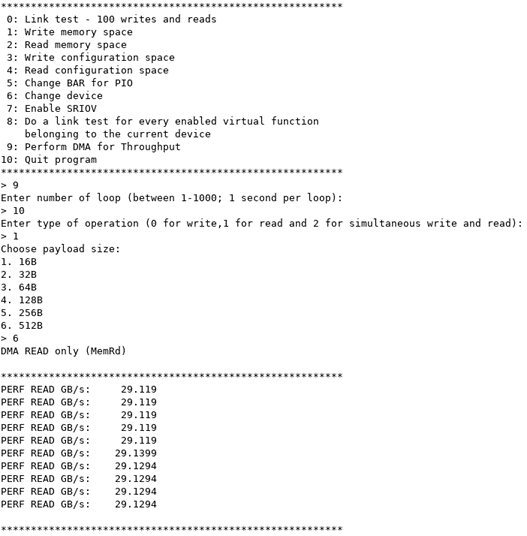

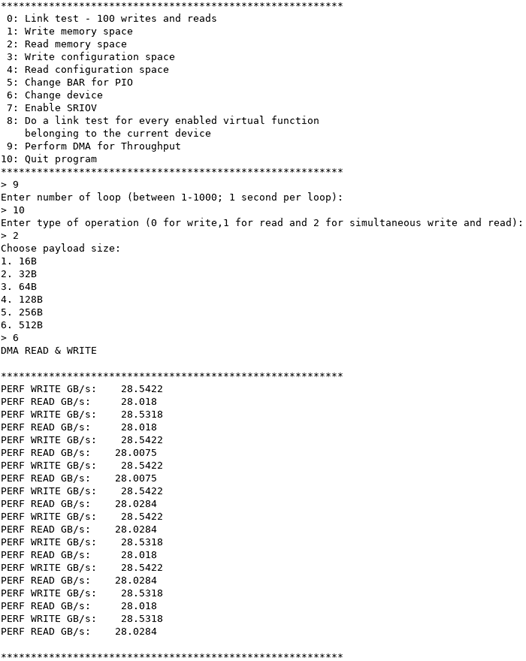

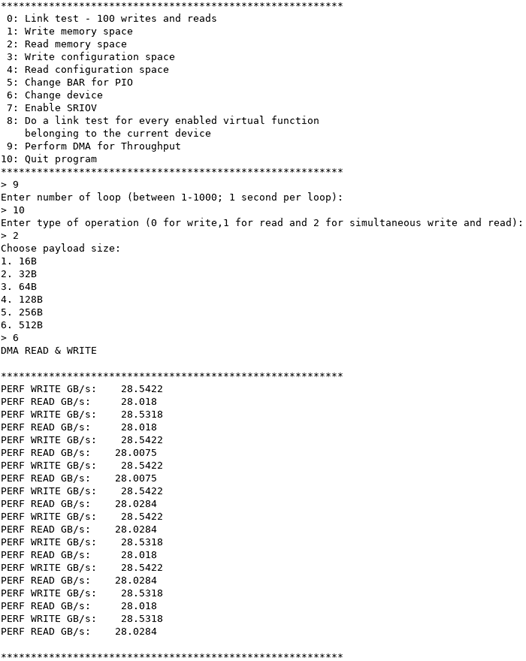

- To perform DMA for throughput test, enter option “9” and press Enter key to proceed.

- Enter number of DMA iterations to be carried out and then press Enter key to select the type of DMA operation, “0” for write operation (device to host), “1” for read operation (host to device) and “2” for simultaneous write and read operations.

- Select payload size for the TLPs used for the throughput test.

Here are block diagrams and sample test results for write only, read only and simultaneous write and read for 10 iterations respectively.

Figure 34. Write Only Operation

Figure 35. Write Only Test Result

Figure 36. Read Only Operation

Figure 37. Read Only Test Result

Figure 38. Simultaneous Write and Read Operation

Figure 39. Simultaneous Write and Read Test Result

Performance Design Example Data Throughput

The following test result is obtained using the hardware and software as mentioned in Hardware and Software Requirements.

The data throughput values may vary especially when a different host system is used.

| TLP Payload Size (Byte) | Data Throughput | |||

|---|---|---|---|---|

| Memory Write (GB/s) | Memory Read (GB/s) | Simultaneous Write and Read | ||

| Write (GB/s) | Read (GB/s) | |||

| 64 | 22.80 | 21.08 | 17.86 | 17.63 |

| 128 | 26.40 | 25.67 | 22.72 | 22.38 |

| 256 | 28.69 | 27.85 | 26.31 | 25.88 |

| 512 | 29.97 | 29.12 | 28.02 | 28.54 |

Note: Data throughput at 16 and 32 bytes TLP payload size does not meet expected throughput values. It may be addressed in the future Quartus® Prime software release.