A newer version of this document is available. Customers should click here to go to the newest version.

38.7.1. Example Description

The example designs are provided in a file called VIC_collateral_cv.zip.

| Example Name | Folder Name | Description |

|---|---|---|

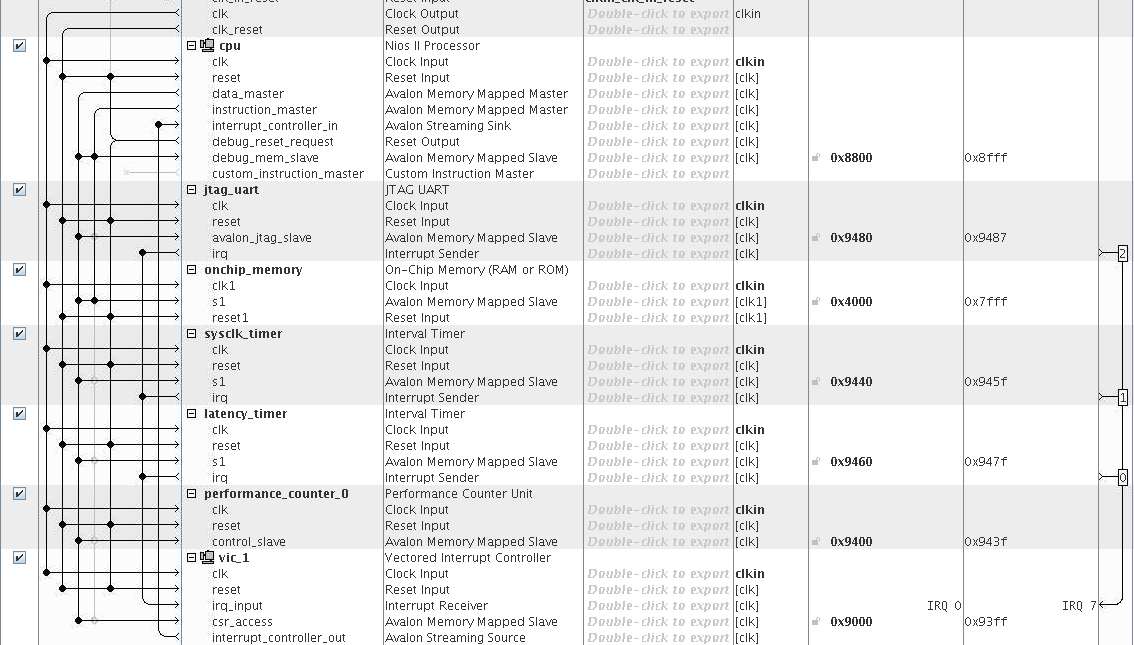

| VIC Basic | VIC_Example | A single VIC |

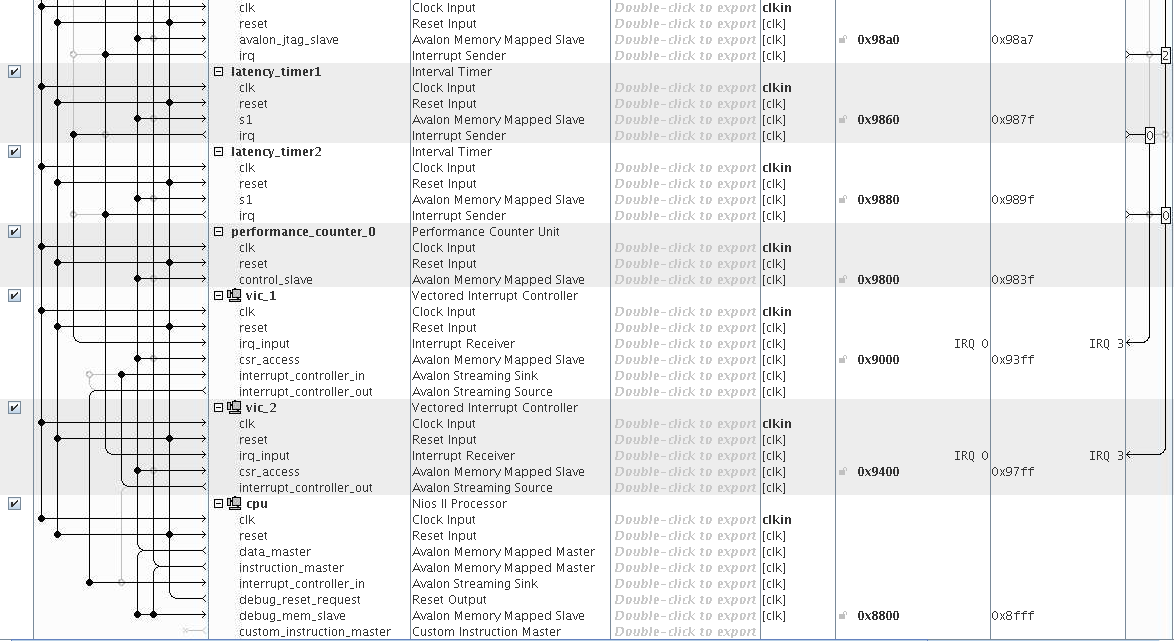

| VIC Daisy-Chain | VIC_DaisyChain_Example | Two daisy-chained VICs |

| VIC Table-Resident | VIC_ISRnVectorTable_Example | VIC with ISR located in vector table |

| IIC | VIC_noVIC_Example | IIC example, for comparison with the VIC examples |

The top-level folder in VIC_collateral_cv.zip, called VIC_collateral_cv, contains the following files:

- run_sw.sh—Shell script to run one, several or all of the examples

- README.txt—Describes the .zip file contents

The IIC design is the same as the VIC Basic design, with the VIC and the EIC interface replaced by the IIC. The VIC Table-Resident design is identical to the VIC Basic design.

In each example, the software uses timers in conjunction with performance counters to measure the interrupt performance. Each example’s software calculates the performance and sends the results to stdout.

VIC_collateral_cv.zip includes a script, run_sw.sh, to run one, several, or all of the example. run_sw.sh downloads the SRAM Object File (.sof) and the Executable and Linkable Format File (.elf) for each example, and executes the code on the Cyclone® V SoC, for the examples that you specify on the command line.