External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP Design Example User Guide

ID

683096

Date

3/29/2021

Public

1. Design Example Quick Start Guide for External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP

2. Design Example Description for External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP

3. Document Revision History for External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP Design Example User Guide

1.1. Creating an EMIF Project

1.2. Generating and Configuring the EMIF IP

1.3. Generating the Synthesizable EMIF Design Example

1.4. Generating the EMIF Design Example for Simulation

1.5. Simulation Versus Hardware Implementation

1.6. Simulating External Memory Interface IP With ModelSim

1.7. Pin Placement for Intel® Cyclone® 10 GX EMIF IP

1.8. Compiling and Programming the Intel® Cyclone® 10 GX EMIF Design Example

1.9. Debugging the Intel® Cyclone® 10 GX EMIF Design Example

1.2. Generating and Configuring the EMIF IP

The following steps illustrate how to generate and configure the EMIF IP. The steps are similar regardless of the memory protocol that you are targeting.

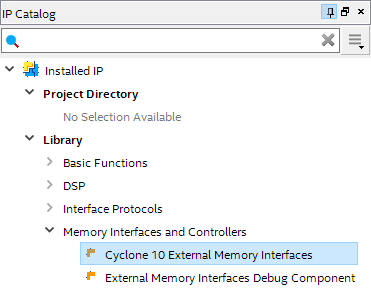

- In the IP Catalog window, select Intel® Cyclone® 10 External Memory Interfaces. (If the IP Catalog window is not visible, select View > Utility Windows > IP Catalog.)

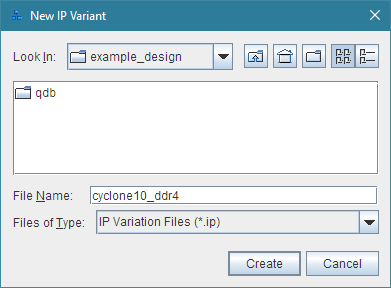

- In the IP Parameter Editor, provide an entity name for the EMIF IP (the name that you provide here becomes the file name for the IP) and specify a directory. Click Create.

- The parameter editor has multiple tabs where you must configure parameters to reflect your EMIF implementation: