Intel® C++ Compiler Classic Developer Guide and Reference

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: GUID-4861A494-8924-4E66-BD34-A9B3FADAA22A

Visible to Intel only — GUID: GUID-4861A494-8924-4E66-BD34-A9B3FADAA22A

Intrinsics for Reading and Writing the Content of Extended Control Registers

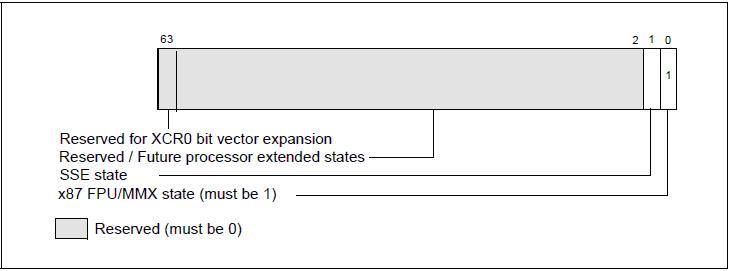

This group of intrinsics includes two intrinsics to read from and write to extended control registers (XCRs). Currently, the only such register defined is XCR0, XFEATURE_ENABLED_MASK register. This register specifies the set of processor states that the operating system enables on that processor, for example x87 FPU states, SSE states, and other processor extended states that Intel® 64 architecture may introduce in the future.

To use these intrinsics, include the immintrin.h file as follows:

#include <immintrin.h>