4.3. Dual Simplex Support

In cases where the TX IP and RX IP use different parameter settings (e.g. data rate, number of lanes L, M, F, S, etc.) or the number of TX and RX channels needed differs, you can use a dual simplex (DS) group to maximize your transceiver channel usage.

For a DS group, you may create an independent simplex TX IP (with one or more channels) and an independent simplex RX IP (with one or more channels) and use the HSSI Support Logic Assignment Editor to fit them into the same transceiver channels. Refer to the GTS Transceiver Dual Simplex Interfaces User Guide for more information.

- Generate the GTS JESD204B TX and RX simplex IP. You can also create a mixed-IP DS group with Serial Lite IV IP or GTS JESD204C IP ( Agilex™ 5 devices only). There are two possible mixed-IP combinations that can be used:

- GTS JESD204B IP + GTS Serial Lite IV IP (both Agilex™ 3 and Agilex™ 5)

- GTS JESD204B IP + GTS JESD204C IP ( Agilex™ 5 only)

Table 14. Possible Combinations for TX IP and RX IP in a DS groupEach combination in the table represents a single DS group. It is possible to have multiple DS groups in the design. IP Combination TX IP RX IP Supported Clocking Mode Single-type IP

(both Agilex™ 3 and Agilex™ 5)

(a) GTS JESD204B IP GTS JESD204B IP System/HVIO PLL or PMA clocking mode Mixed-type IP: JESD204B IP + GTS Serial Lite IV IP

(both Agilex™ 3 and Agilex™ 5)

(b) GTS JESD204B IP GTS Serial Lite IV IP System/HVIO PLL only (c) GTS Serial Lite IV IP GTS JESD204B IP System/HVIO PLL only Mixed-type IP: JESD204B IP + GTS JESD204C IP

( Agilex™ 5 only)

(d) GTS JESD204B IP GTS JESD204C IP System/HVIO PLL or PMA clocking mode (e) GTS JESD204C IP GTS JESD204B IP System/HVIO PLL or PMA clocking mode - Select System/HVIO PLL in the Clocking mode option in IP GUI main tab to allow merging between GTS JESD204B and Serial Lite IV IP ((b) and (c)). When using GTS JESD204B IP only ((a)) or GTS JESD204B IP and GTS JESD204C IP ((d) and (e)) combination in the same DS group, both System/HVIO PLL and PMA clocking modes are supported.

- Configure the System/HVIO PLL frequency parameter according to the formula described in GTS JESD204B IP Core Clocks.

Note:The System/HVIO PLL is shared between TX and RX IPs in dual simplex mode. Using different data rates for TX and RX in dual simplex mode will result in having different System/HVIO PLL frequencies required for both TX and RX channels. In this scenario, use the highest frequency calculation for the System/HVIO PLL output. Refer to the GTS Transceiver Dual Simplex Interfaces User Guide for more information on the System/HVIO PLL frequency calculation.

The reference clock frequency selection should be selected based on the highest System/HVIO PLL frequency. The reference clock frequency is the same for both simplex IPs as they are sharing the same System/HVIO PLL. Configure the TX and RX IP to have the same reference clock in the IP parameter editor. For the GTS JESD204B IP, the reference clock is configured via the PLL/CDR Reference Clock Frequency parameter by selecting the available frequency option. Ensure refclk is also supplied with this frequency at the refclk input of the System/HVIO PLL.

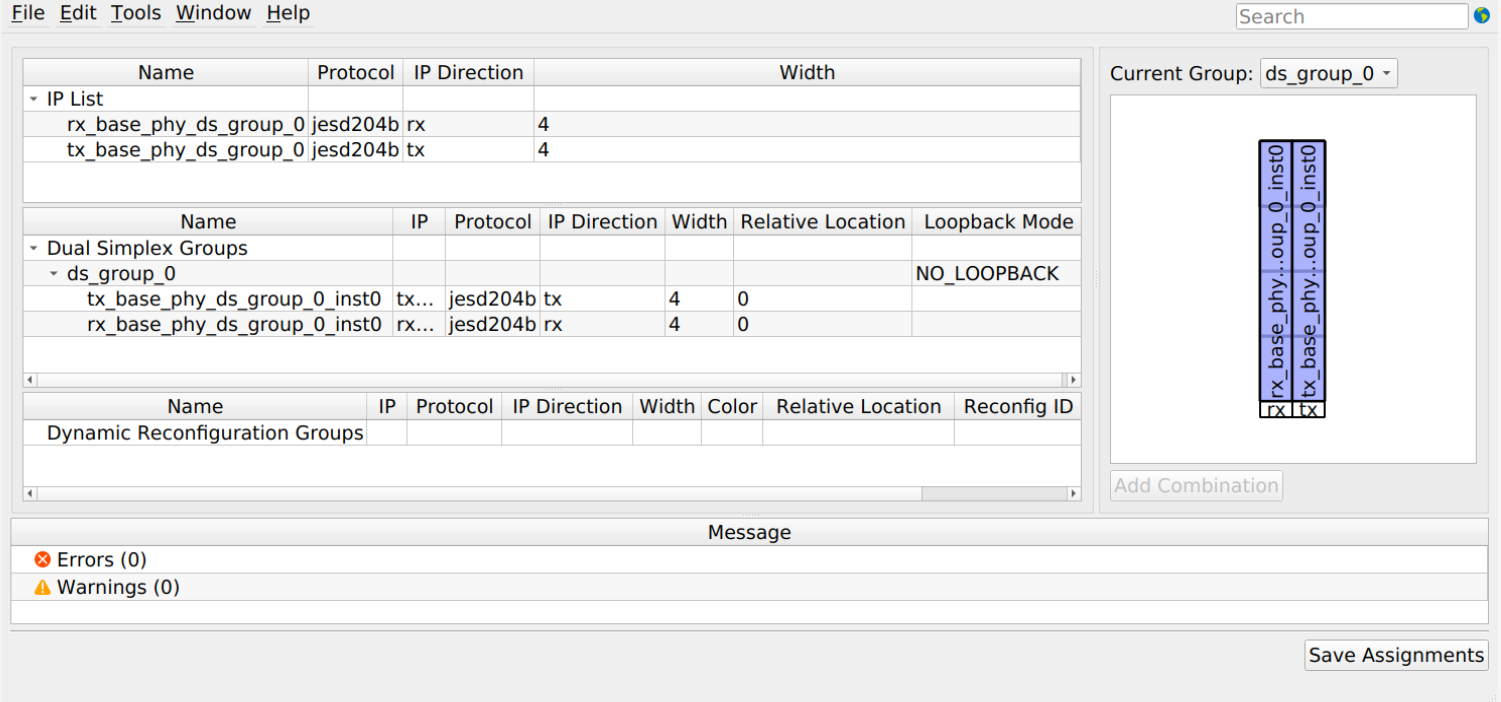

Note: When creating a DS group with JESD204B and Serial Lite IV, RS-FEC mode must be disabled in the Serial Lite IV IP. - Provide location of each simplex IP in a DS group relative to the starting channel location in the HSSI Support Logic Assignment Editor. To do this, open the HSSI Support Logic Assignment Editor in Quartus® Prime by selecting Assignments > HSSI Support Logic Assignment Editor.

- Assign your individual simplex IPs to a dual simplex (DS) group by right-clicking your IP component under the IP > Click Create Instance in… > Select or create a new DS group.

Figure 11. HSSI Support Logic Assignment Editor

The HSSI Support Logic Assignment Editor does a quick legality check (protocol level and attribute level) to see if the simplex IPs assigned to a dual simplex group are compatible. If the simplex IPs are not compatible, error messages will be prompted.

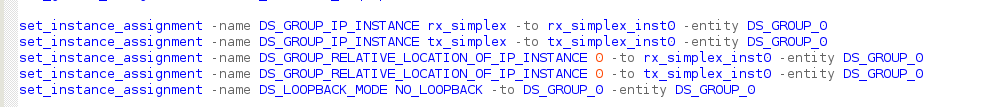

- After assigning simplex IPs to a DS group, save the assignments. When you save the DS group, the QSF assignments are added automatically to the project QSF. For example:

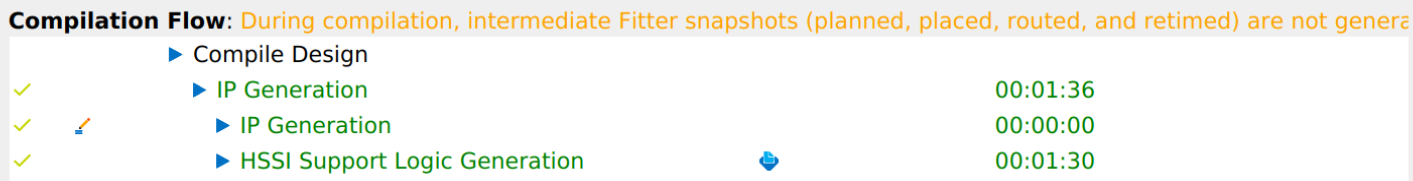

- Run the HSSI Dual Simplex IP Generation in the Compilation Dashboard to obtain a new DS IP:

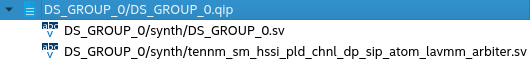

- Connect the generated DS IP to the rest of your design logic:

This DS IP (DS_GROUP_0) contains the ports of both the TX and RX simplex IPs created in step 1 in a single module. It also merges the ports associated with the reset sequencer and System/HVIO PLL (if used) in the same module.

You can now instantiate this module in your design. You may obtain the instantiation template of DS_GROUP_0 in the following files:

- Verilog: <Quartus project folder>/DS_GROUP_0/DS_GROUP_0_inst.v

- VHDL: <Quartus project folder>/DS_GROUP_0/DS_GROUP_0_inst.vhd

Perform the required connections. If you have selected System PLL clocking mode earlier, connect the output of the System PLL to the sysclk port of the DS_GROUP_0 module. If you have selected HVIO PLL clocking mode, connect the output outclk_0 and locked signals of the HVIO PLL to the sysclk and syspll_locked ports of the DS_GROUP_0 module respectively.

Refer to the GTS Transceiver Dual Simplex Interfaces User Guide for more info on performing the connections.

The Dual Simplex support for the GTS JESD204B IP in current release of the Quartus® Prime software is limited to:

- A DS group can only contain one Simplex TX IP (JESD204B/JESD204C/Serial Lite IV) and one Simplex RX IP (JESD204B/JESD204C/Serial Lite IV).

- Simulation and hardware supports up to L=4 only.

- Refclk recovery (Clkrx) feature is not supported in dual simplex mode for this release.