A newer version of this document is available. Customers should click here to go to the newest version.

2.7. Retrieving SEU Statistics using Mailbox Command

READ_SEU_STATS (0x40)

Examples of the READ_SEU_STATS (0x40) Mailbox Command:

To retrieve the SEU statistics via the Configuration Debugger tool, you can send 0x40 as the Command Code and 0x30000 in the Parameter List field.

0x30000 refers to the sector 0x3, which is the same sector as the injected SEU error.

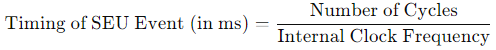

The SEU statistics are measured in cycles. To obtain the timing of SEU event, use the following equation to convert the number of cycles into milliseconds (ms):

| Configuration Clock Source | Internal Clock Frequency |

|---|---|

| Internal oscillator | 160–230 MHz |

| External configuration clock source (OSC_CLK_1) | 200 MHz for low-powered devices. OPN with core speed 6 and power S/X. For example, A5Exxxxxxxxxx6Sxx and A5Exxxxxxxxxx6Xxx |

| 250 MHz for other Agilex™ 5 devices. |

For example:

The T_seu_cycle is 0x000B991C in hexadecimal and it is equals to 0x760,092 in decimal. To convert 760,092 cycles into milliseconds at a frequency of 200 MHz, the timing of SEU event obtained is as follows:

T_seu_cycle = 760,092 cycles / 200 MHz = 3.80046 ms

| SEU Statistic | Description |

|---|---|

| T_seu_cycle | The time between the start of the most recent SEU detection cycle to the previous cycle. |

| T_seu_detect | The most recent time spent in performing the SEU detection within a SEU cycle. |

| T_seu_correct | The most recent time spent in performing the SEU correction (internal scrubbing) within a SEU cycle if a correctable error is detected. 0x FFFFFFFF if no correction is done. |

| T_seu_inject_detect | The most recent duration from the SEU error being injected to the time the SEU is detected. 0x FFFFFFFF if no injection is done. |

| T_sdm_seu_poll_interval | The time between the start of the most recent SDM check cnoc_return_interrupt line (if there is an SEU error) to the previous one. Use T_sdm_seu_poll_interval to measure the SDM SEU error polls interval. |

| T_sdm_seu_pin_toggle_overhead | The time for SDM to toggle the SEU_ERROR pin after SDM detects error when polling the SEU error (check_cnoc_return_interrupt). |

- To obtain SEU Inject to Detect Cycle (best case), inject a safe SEU error by sending this mailbox command: INSERT_SAFE_SEU_ERROR [0x41] with the T=01 option (inject before next detection cycle), followed by sending READ_SEU_STATS [0x40].

- To obtain SEU Inject to Detect Cycle (worst case), send the INSERT_SAFE_SEU_ERROR [0x41] mailbox command with the T=10 option (inject after next detection/correction cycle).