AXI Streaming Intel® FPGA IP for PCI Express* User Guide

ID

790711

Date

1/24/2025

Public

1. Introduction

2. Features

3. Getting Started with the AXI Streaming Intel® FPGA IP for PCI Express*

4. IP Architecture and Functional Description

5. AXI Streaming Intel® FPGA IP for PCI Express* Parameters

6. Interfaces and Signals

7. Register Descriptions

8. Document Revision History for the AXI Streaming Intel® FPGA IP for PCI Express* User Guide

A. Specifications

B. Simulating the Design Example

1.1. Goal of the AXI Streaming Intel® FPGA IP for PCI Express* User Guide

1.2. Intended Audience for the AXI Streaming Intel® FPGA IP for PCI Express* User Guide

1.3. What is PCI Express* ?

1.4. What are the Intel® FPGA IPs for PCI Express* ?

1.5. What is the AXI Streaming Intel® FPGA IP for PCI Express* ?

1.6. Example Use Models

1.7. Design Flow Requirements

3.1. Download and Install Quartus Software

3.2. Obtain and Install Intel FPGA IPs and Licenses

3.3. Configure and Generate the AXI Streaming Intel® FPGA IP for PCI Express*

3.4. About the AXI Streaming Intel® FPGA IP for PCI Express Design Examples

3.5. Instantiate and Connect the AXI Streaming Intel® FPGA IP for PCI Express* Interfaces

3.6. Simulate the AXI Streaming Intel® FPGA IP for PCI Express* IP Variant

3.7. Compile the AXI Streaming Intel® FPGA IP for PCI Express* IP Variant

3.8. Software Drivers for AXI Streaming Intel® FPGA IP for PCI Express* IP Variant

3.9. Build the Application for the AXI Streaming Intel® FPGA IP for PCI Express* IP Variant

3.10. Verification with the AXI Streaming Intel® FPGA IP for PCI Express* IP Variant

3.11. Debugging with the AXI Streaming Intel® FPGA IP for PCI Express* IP Variant

4.1. Clocks and Resets

4.2. PCIe Hard IP (HIP)

4.3. HIP Interface (IF) Adaptor

4.4. Application Error Reporting

4.5. Debug Toolkit and Hard IP (HIP) Reconfiguration Interface

4.6. Configuration Space Extension

4.7. Control Shadow

4.8. Configuration Intercept Interface

4.9. Power Management

4.10. Legacy Interrupt

4.11. Credit Handling

4.12. Completion Timeout

4.13. Transaction Ordering

4.14. Page Request Service (PRS) Events

4.15. TX Non-Posted Metering Requirement on Application

4.16. MSI Pending

4.17. D-State Status

4.18. Configuration Retry Status Enable

4.19. AXI-Streaming Interface

4.20. Precision Time Measurement (PTM)

6.1. Overview

6.2. Clocks and Resets

6.3. Application Packet Interface

6.4. Configuration Extension Bus Interface

6.5. Configuration Intercept Interface

6.6. Function Level Reset Interface

6.7. Control Shadow Interface (st_ctrlshadow)

6.8. Completion Timeout Interface (st_cplto)

6.9. Miscellaneous Signals

6.10. Control and Status Register Responder Interface (lite_csr)

6.11. Error Interface (st_err)

6.12. VF Error Flag Interface (vf_err/sent_vfnonfatalmsg)

6.13. VIRTIO PCI* Configuration Access Interface

6.14. Serial Data Signals

7.3.1.1. AXI Streaming Intel® FPGA IP for PCI Express* Version

7.3.1.2. AXI Streaming Intel® FPGA IP for PCI Express* Features

7.3.1.3. AXI Streaming Intel® FPGA IP for PCI Express* Interface Attributes

7.3.1.4. HOT PLUG GEN CTRL

7.3.1.5. POWER MANAGEMENT CTRL

7.3.1.6. LEGACY INTERRUPT CTRL

7.3.1.7. CFG REG IA CTRL

7.3.1.8. CFG REG IA FN NUM

7.3.1.9. CFG REG IA WRDATA

7.3.1.10. CFG REG IA RDDATA

7.3.1.11. PRS CTRL

7.3.1.12. MSI PENDING CTRL

7.3.1.13. MSI PENDING

7.3.1.14. D-STATE STS

7.3.1.15. CFG RETRY CTRL

7.3.3.1. PERFMON CTRL

7.3.3.2. TX MRD TLP

7.3.3.3. TX MWR TLP

7.3.3.4. TX MSG TLP

7.3.3.5. TX CFGWR TLP

7.3.3.6. TX CFGRD TLP

7.3.3.7. RX MRD TLP

7.3.3.8. RX MWR TLP

7.3.3.9. RX MSG TLP

7.3.3.10. RX CFGWR TLP

7.3.3.11. RX CFGRD TLP

7.3.3.12. TX MEM DATA

7.3.3.13. TX CPL DATA

7.3.3.14. RX MEM DATA

7.3.3.15. RX CPL DATA

3.4. About the AXI Streaming Intel® FPGA IP for PCI Express Design Examples

For more details on your generated AXI Streaming IP design example, refer to the sections below.

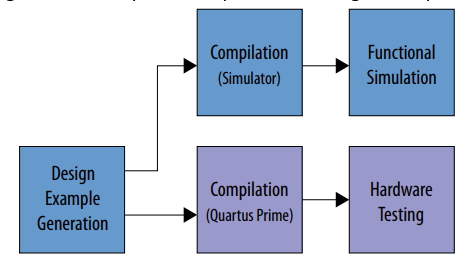

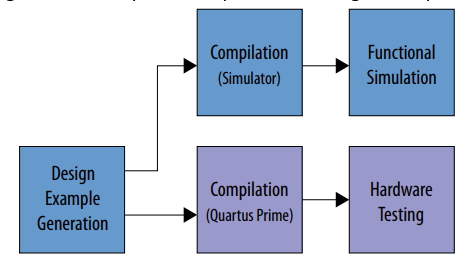

Figure 6. Development Steps for the Design Example

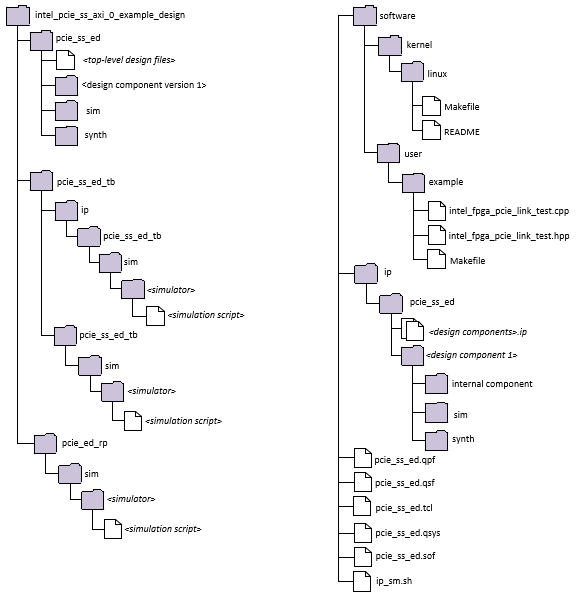

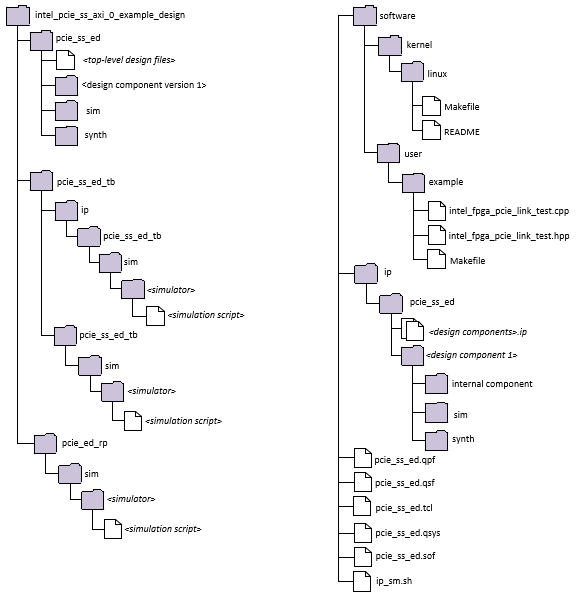

Figure 7. AXI Streaming Intel® FPGA IP for PCI Express Design Example Directory Structure

The following table presents an overview of the design examples supported by the AXI Streaming Intel® FPGA IP for PCI Express. For detailed information on the supported configuration for the PIO design example, refer to Functional Description for the Programmed Input/Output (PIO) Design Example.

Note: The SR-IOV and Performance design examples are not supported in this release. Ignore the selections for these design examples in the IP Parameter Editor.

| Design Example | Hard IP Mode | Simulators Supported | Development Kits Supported |

|---|---|---|---|

| PIO |

|

VCS, VCSMX, Questasim, and Modelsim | Agilex™ 7 I-Series FPGA Development Kit ES |