F-Tile 25G Ethernet Intel® FPGA IP Design Example User Guide

ID

750200

Date

1/24/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. Quick Start Guide

2. F-Tile 25G Ethernet Single-Channel Design Example

3. F-Tile 25G Ethernet Single Channel Design Example with Dynamic Reconfiguration

4. F-Tile 25G Ethernet Intel FPGA IP Design Example User Guide Archives

5. Document Revision History for F-Tile 25G Ethernet Intel® FPGA IP Design Example User Guide

1.1. Directory Structure

1.2. Generating the Design Example

1.3. Generating Tile Files

1.4. Simulating the F-Tile 25G Ethernet Intel® FPGA IP Design Example Testbench

1.5. Compiling and Configuring the Design Example in Hardware

1.6. Testing the F-Tile 25G Ethernet Intel® FPGA IP Hardware Design Example

3.5.1. Test Procedure

Follow these steps to test the design examples in hardware:

- In system console, change the directory to <design_example_dir>/hardware_test_design/hwtest.

- Run the following command: source main.tcl to select a JTAG master.

- To select the JTAG master for Agilex™ 7 devices, run this command: set_jtag <number of appropriate JTAG master>. Example: set_jtag 1.

- Run the following commands in the system console to start the dynamic reconfiguration test: source altera/sval_top/dr_f_10g_test.tcl . The following are executed in the dr_f_10g_test.tcl script:

Table 11. Command Parameters Parameter Description Example Usage chkphy_status <link num> Displays the clock frequencies and PHY lock status. % chkphy_status 0 # Check status of link 0 chkmac_stats <link num> Displays the values in the MAC statistics counters. % chkmac_stats 1 # Checks mac statistics counter of link 1 clear_all_stats <link num> Clears the IP core statistics counters. % clear_all_stats 1 # Clears statistics counter of link 1 start_gen <link num> Starts the packet generator. % start_gen 1 # Begin packet generation on link 1 stop_gen <link num> Stops the packet generator. % stop_gen 1 # Stop packet generation on link 1 loop_on <link num> Turns on internal serial loopback. % loop_on 2 # Turn on internal loopback on link 2 loop_off <link num> Turns off internal serial loopback. % loop_off 2 # Turn off internal loopback on link 2 reg_read <addr> Returns the IP core register value at <addr>. % reg_read 0x302 # Read IP CSR register at address 302 of link 0 % reg_read 0x4542 # Read transceiver reconfiguration register at address 4542 of link 0

reg_write <addr> <data> Writes <data> to the IP core register at address <addr>. % reg_write 0x30301 0x1 # Write 0x1 to IP CSR scratch register at address 301 of link 3 % reg_write 0x34542 0x0 # Write 0x0 to transceiver reconfiguration register at address 4542 of link 3

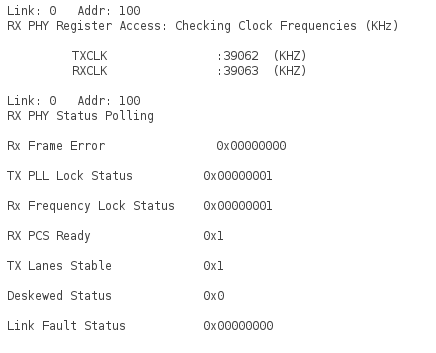

- Type chkphy_status <link num> to check the status of the PHY. The TXCLK, RXCLK, and RX status should have the same values shown below for a stable link:

Figure 10. System Console Example Printout

- Type chkphy_status <link num> to check the status of the PHY. The TXCLK, RXCLK, and RX status should have the same values shown below for a stable link:

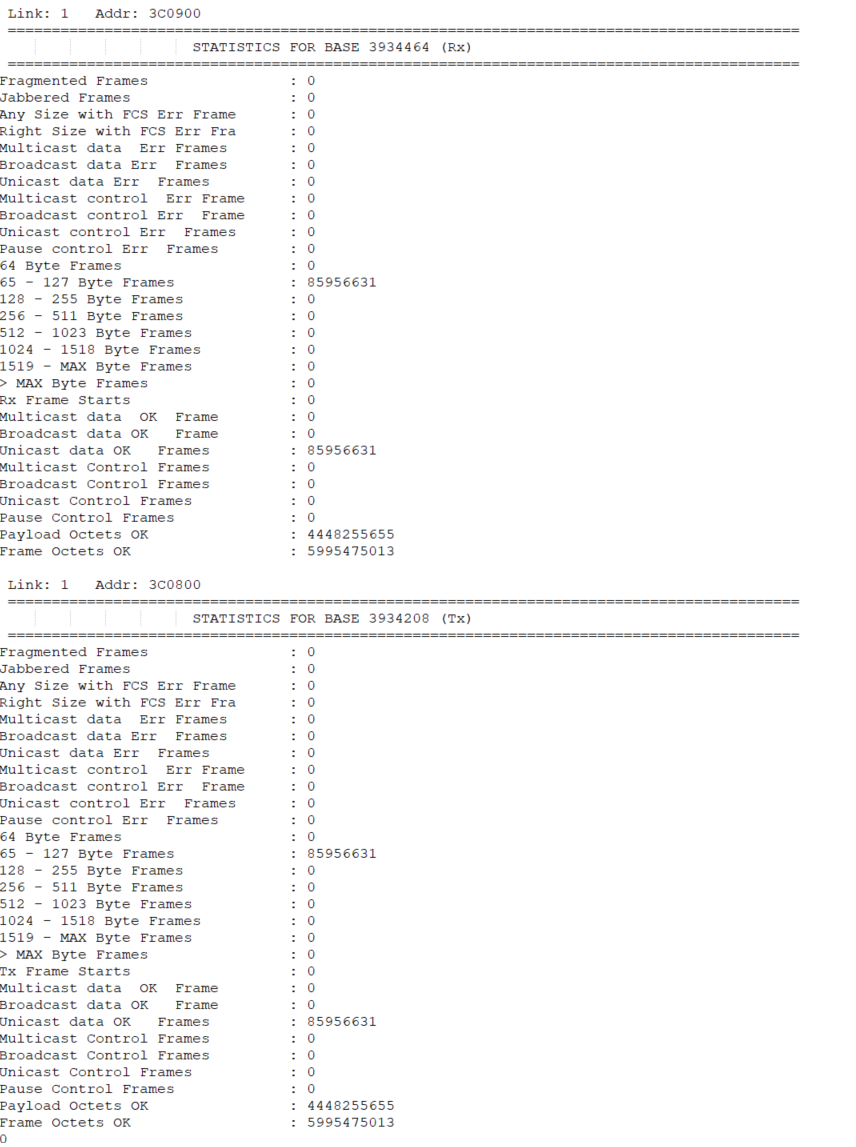

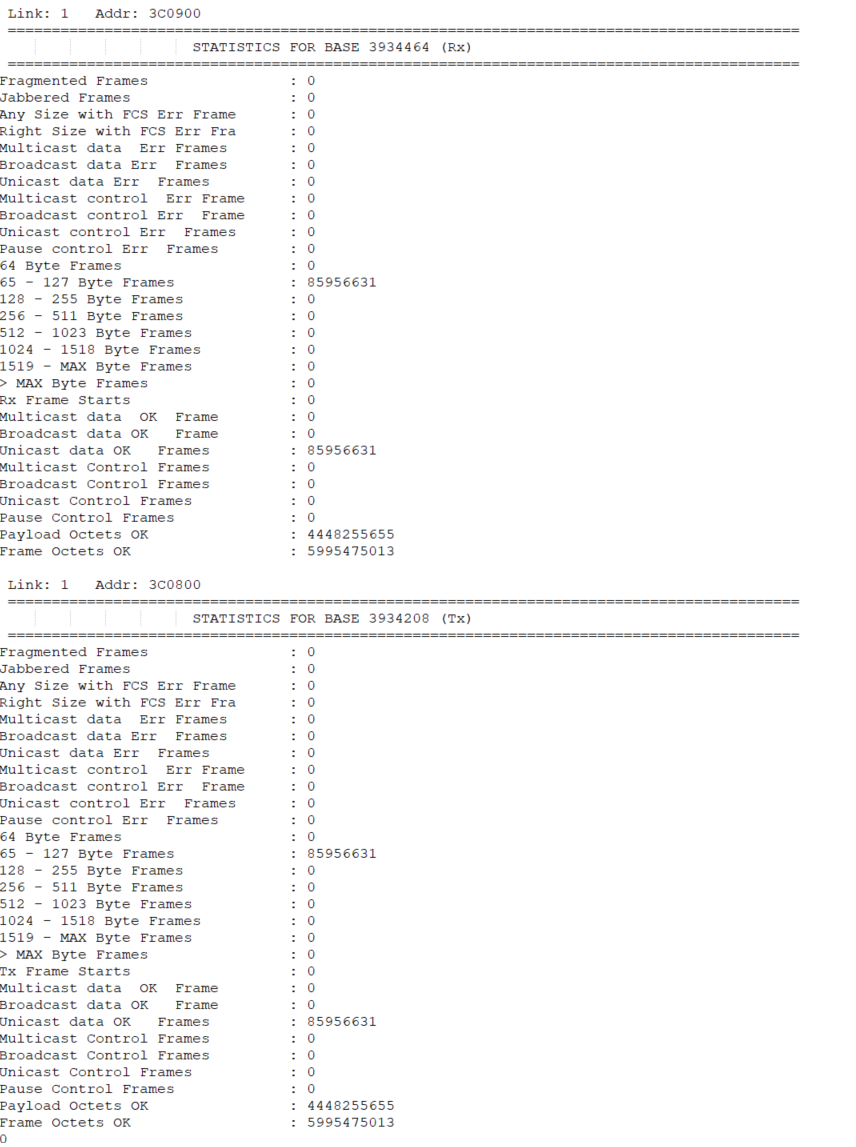

Figure 11. Sample Test Output—TX and RX Statistics Counters