Questa*-Intel® FPGA Edition Quick-Start: Intel® Quartus® Prime Pro Edition

ID

691278

Date

6/26/2022

Public

1.7. View Signal Waveforms

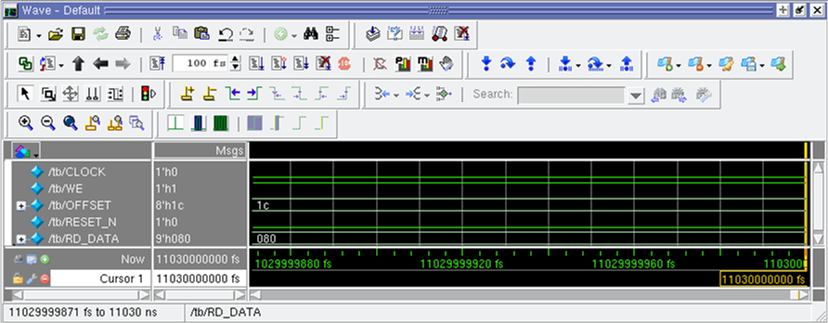

Follow these steps to view signals in the testbench_1.v simulation waveform:

- Click the Wave window. The simulation waveform ends at 11030 ns, as the testbench specifies. The Wave window lists the CLOCK, WE, OFFSET, RESET_N, and RD_DATA signals.

Figure 7. Questa* Intel® FPGA Edition Wave Window

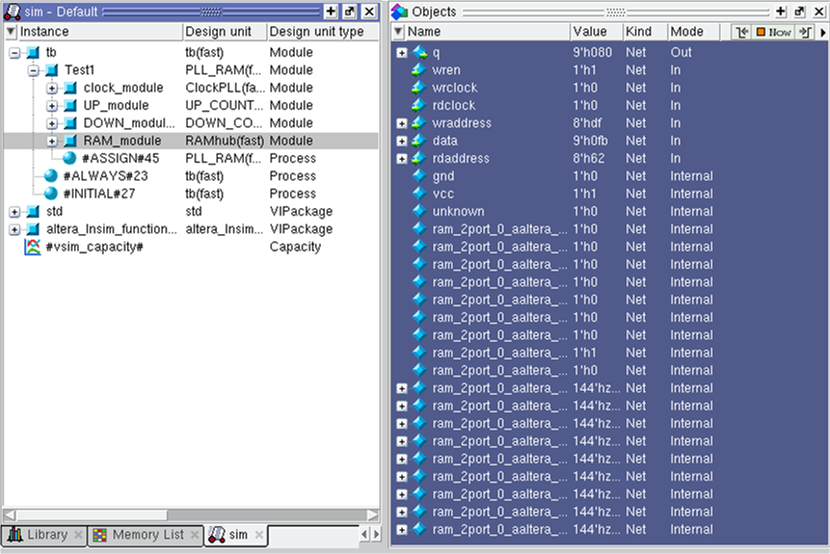

- Click the Sim tab to view the signals in the top-level pll_ram.v design. The Sim window synchronizes with the Objects window.

- Expand the tb folder in the sim tab to view the top-level module signals.

- Expand the Test1 folder. The Objects window displays UP_module, DOWN_module, PLL_module, and RAM_module signals.

- In the Sim window, select a module under Test1 to display the module's signals in the Objects window.

Figure 8. Questa* Intel® FPGA Edition Sim and Objects Windows

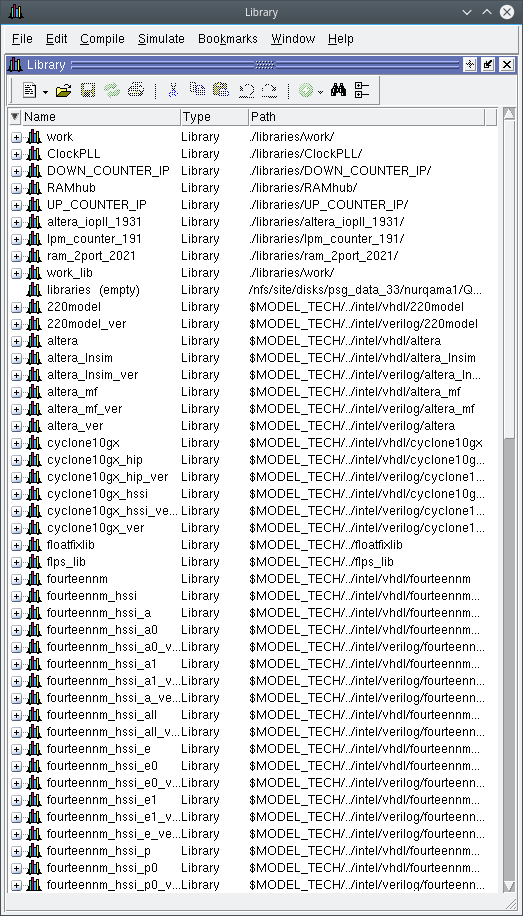

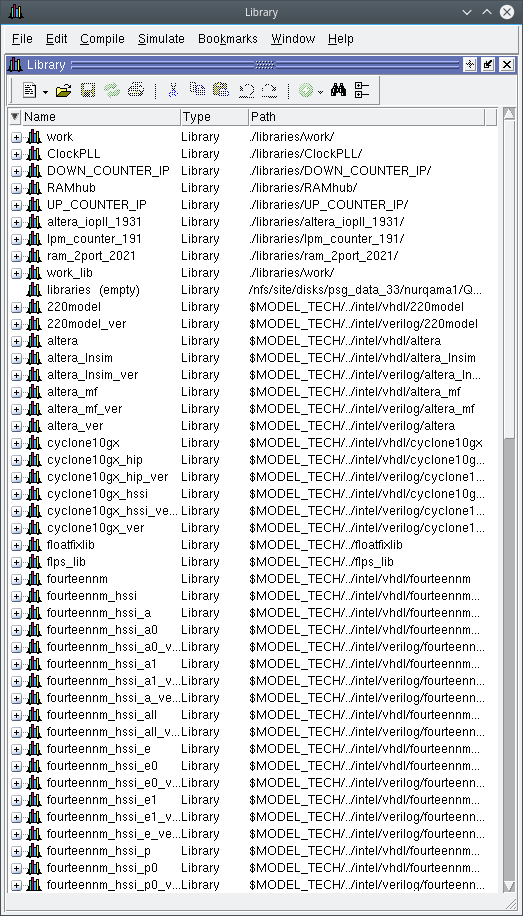

- View the simulation library files in the Library window.

Figure 9. Questa* Intel® FPGA Edition Library Window