8.2.3. High-Speed Streaming (HS ST) Debug Interface IP

The High-Speed Streaming (HS ST) Debug Interface IP communicates with the internal debug hardware of an FPGA device through an Avalon® memory-mapped interface instead of the JTAG pin connections. You can create a debug host connection to an FPGA device without requiring a physical connection to the FPGA JTAG pins.

By skipping the physical connection, you remove the need for physical JTAG pin access, which can potentially increase the security of your device.

The HS ST Debug Interface IP is available in the Quartus® Prime Pro Edition IP Catalog:IP Catalog > Basic Functions > Simulation, Debug and Verification > Debug and Performance > HS ST Debug Interface IP

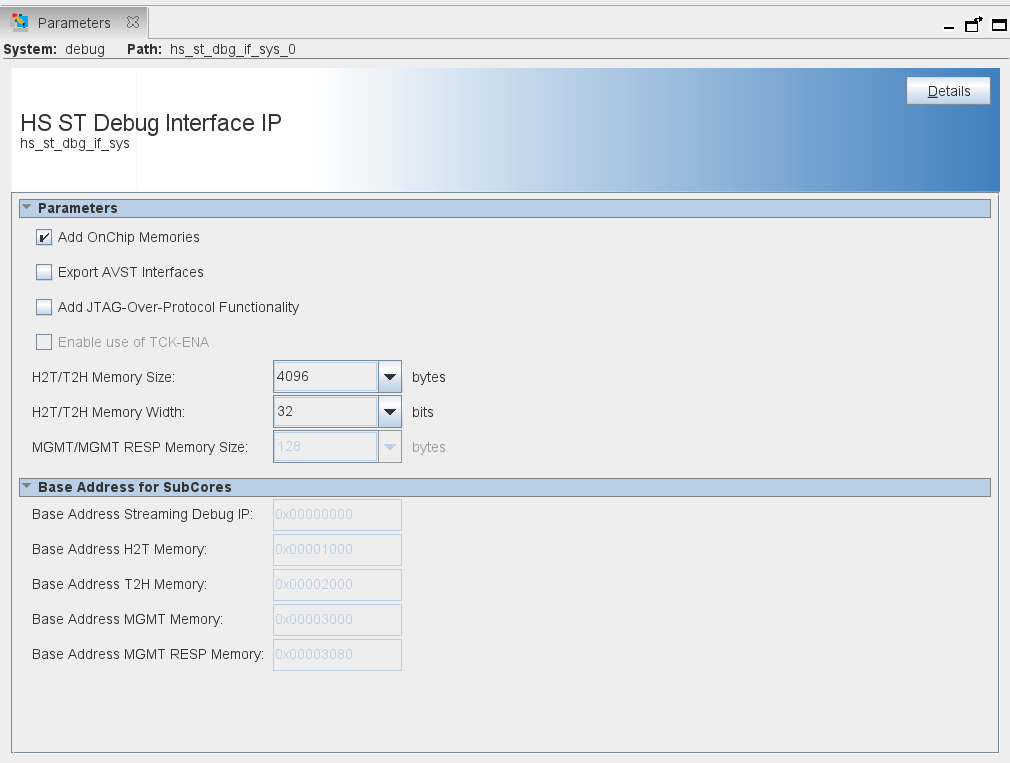

| Parameter | Description |

|---|---|

| Add OnChip Memories | Include OnChip Memories in the IP for H2T/T2H and MGMT/MGMT-RESP instructions. |

| Export AVST Interfaces | Export H2T/T2H, MGMT/MGMT-RESP AVST Interfaces, allowing user to manually connect. |

| Add JTAG-Over-Protocol Functionality | Enable JTAG Over Protocol, removing JTAG logic access via JTAG pins. |

| Enable use of TCK-ENA | This option is only available when JOP functionality is enabled. When this option is not enabled, the TCK frequency is generated by gating the input clock of the JOP IP. Closing with timing with a gated clock can cause challenges. Enable this option to help close timing if you are having problems. However, not all JTAG-based logic works with this option enabled. |

| H2T/T2H Memory Size | Sets the depth of the H2T/T2H memories in the IP. |

| H2T/T2H Memory Width | Sets the width of the H2T/T2H memories in the IP. |

| MGMT/MGMT RESP Memory Size | Sets the size of the MGMT/MGMT RESP memory |

The HS ST Debug Interface IP interface consists of the following elements:

- Clock Input

- Reset Input

- Avalon® memory-mapped interface agent interface

- The Avalon® memory-mapped interface data width is determined by the H2T/T2H Memory Width parameter.