Visible to Intel only — GUID: zqn1600772341695

Ixiasoft

3.2. Generating a 5G Polar IP

To include the IP in a design, generate the IP in the Intel® Quartus® Prime software. Or optionally, you can generate a design example that includes the generated IP, a C model, a MATLAB model, and simulation scripts.

- Create a New Intel® Quartus® Prime project

- Open IP Catalog.

- Select DSP > FEC > 5G Polar and click Add

- Enter a name for your IP variant and click Create.

The name is for both the top-level RTL module and the corresponding .ip file.The parameter editor for this IP appears.

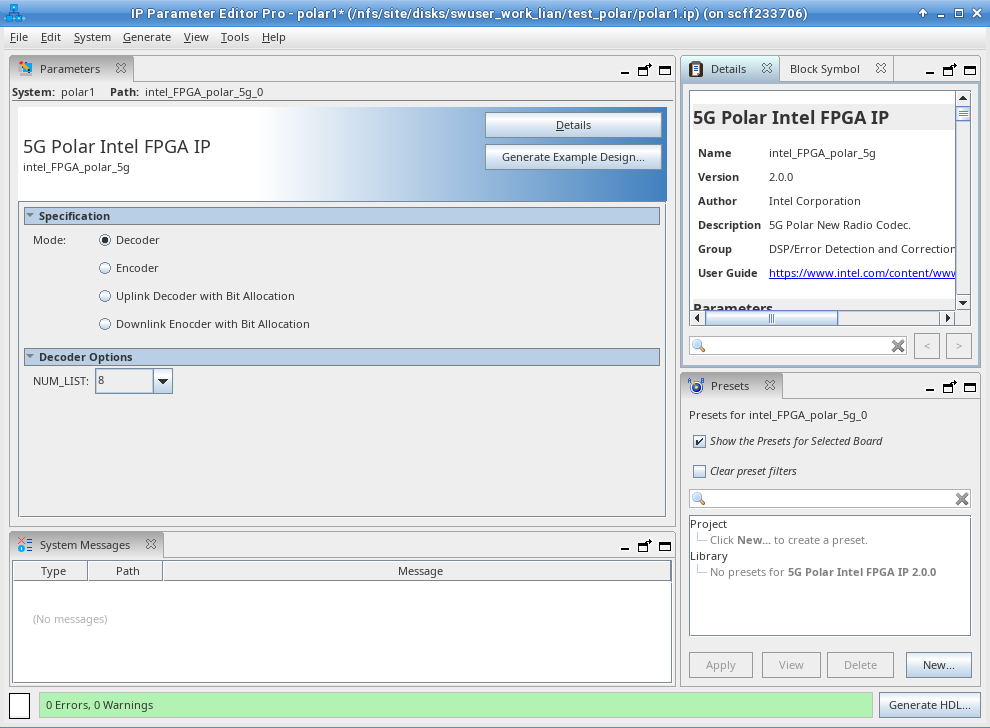

- Choose your parameters.

Table 6. 5G Polar Parameters Parameter Name Values Description Mode Encoder

Decoder

Uplink Decoder with Bit Allocation

Downlink Encoder with Bit Allocation

Select between encoder, decoder, uplink decoder with bit allocation, or downlink encoder with bit allocation. NUM_LIST 4

8

List size of the polar list decoder. Figure 3. 5G Polar Parameter Editor

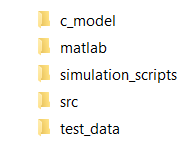

- For an optional design example, click Generate Example Design

The software creates a design example.Figure 4. Design Example Directory Structure

- Click Generate HDL.

Intel® Quartus® Prime generates the RTL and the files necessary to instantiate the IP in your design and synthesize it.

Related Information