1.5. Test Results

The following table contains the possible results and their definition.

| Result | Definition |

|---|---|

| PASS |

The Device Under Test (DUT) was observed to exhibit conformant behavior. |

| PASS with comments |

The DUT was observed to exhibit conformant behavior. However, an additional explanation of the situation is included, such as due to time limitations only a portion of the testing was performed. |

| FAIL |

The DUT was observed to exhibit non-conformant behavior. |

| Warning |

The DUT was observed to exhibit behavior that is not recommended. |

| Refer to comments |

From the observations, a valid pass or fail could not be determined. An additional explanation of the situation is included. |

The following table shows the results for test cases CGS.1, CGS.2, ILA.1, ILA.2, ILA.3, TL.1, and SCR.1 with different values of L, M, F, K, subclass, data rate, sampling clock, link clock and SYSREF frequencies.

| Test |

L |

M |

F |

Subclass |

SCR |

K |

Data rate (Gbps) |

ADC Sampling Clock (MHz) |

Link Clock (MHz) |

Result |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 |

1 |

1 |

2 |

1 |

0 |

16 |

12.5 |

625 |

312.5 |

PASS |

| 2 |

1 |

1 |

2 |

1 |

1 |

16 |

12.5 |

625 |

312.5 |

PASS |

| 3 |

1 |

1 |

2 |

1 |

0 |

32 |

12.5 |

625 |

312.5 |

PASS |

| 4 |

1 |

1 |

2 |

1 |

1 |

32 |

12.5 |

625 |

312.5 |

PASS |

| 5 |

2 |

1 |

1 |

1 |

0 |

20 |

12.5 |

1250 |

312.5 |

PASS |

| 6 |

2 |

1 |

1 |

1 |

1 |

20 |

12.5 |

1250 |

312.5 |

PASS |

| 7 |

2 |

1 |

1 |

1 |

0 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 8 |

2 |

1 |

1 |

1 |

1 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 9 |

2 |

1 |

2 |

1 |

0 |

16 |

12.5 |

1250 |

312.5 |

PASS |

| 10 |

2 |

1 |

2 |

1 |

1 |

16 |

12.5 |

1250 |

312.5 |

PASS |

| 11 |

2 |

1 |

2 |

1 |

0 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 12 |

2 |

1 |

2 |

1 |

1 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 13 |

4 |

1 |

1 |

1 |

0 |

20 |

6.25 |

1250 |

156.25 |

PASS |

| 14 |

4 |

1 |

1 |

1 |

1 |

20 |

6.25 |

1250 |

156.25 |

PASS |

| 15 |

4 |

1 |

1 |

1 |

0 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 16 |

4 |

1 |

1 |

1 |

1 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 17 |

4 |

1 |

2 |

1 |

0 |

16 |

6.25 |

1250 |

156.25 |

PASS |

| 18 |

4 |

1 |

2 |

1 |

1 |

16 |

6.25 |

1250 |

156.25 |

PASS |

| 19 |

4 |

1 |

2 |

1 |

0 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 20 |

4 |

1 |

2 |

1 |

1 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 21 |

8 |

1 |

1 |

1 |

0 |

20 |

3.125 |

1250 |

78.125 |

PASS |

| 22 |

8 |

1 |

1 |

1 |

1 |

20 |

3.125 |

1250 |

78.125 |

PASS |

| 23 |

8 |

1 |

1 |

1 |

0 |

32 |

3.125 |

1250 |

78.125 |

PASS |

| 24 |

8 |

1 |

1 |

1 |

1 |

32 |

3.125 |

1250 |

78.125 |

PASS |

| 25 |

8 |

1 |

2 |

1 |

0 |

16 |

3.125 |

1250 |

78.125 |

PASS |

| 26 |

8 |

1 |

2 |

1 |

1 |

16 |

3.125 |

1250 |

78.125 |

PASS |

| 27 |

8 |

1 |

2 |

1 |

0 |

32 |

3.125 |

1250 |

78.125 |

PASS |

| 28 |

8 |

1 |

2 |

1 |

1 |

32 |

3.125 |

1250 |

78.125 |

PASS |

| 29 |

1 |

2 |

4 |

1 |

0 |

16 |

12.5 |

312.5 |

312.5 |

PASS |

| 30 |

1 |

2 |

4 |

1 |

1 |

16 |

12.5 |

312.5 |

312.5 |

PASS |

| 31 |

1 |

2 |

4 |

1 |

0 |

32 |

12.5 |

312.5 |

312.5 |

PASS |

| 32 |

1 |

2 |

4 |

1 |

1 |

32 |

12.5 |

312.5 |

312.5 |

PASS |

| 33 |

2 |

2 |

2 |

1 |

0 |

16 |

12.5 |

625 |

312.5 |

PASS |

| 34 |

2 |

2 |

2 |

1 |

1 |

16 |

12.5 |

625 |

312.5 |

PASS |

| 35 |

2 |

2 |

2 |

1 |

0 |

32 |

12.5 |

625 |

312.5 |

PASS |

| 36 |

2 |

2 |

2 |

1 |

1 |

32 |

12.5 |

625 |

312.5 |

PASS |

| 37 |

4 |

2 |

1 |

1 |

0 |

20 |

12.5 |

1250 |

312.5 |

PASS |

| 38 |

4 |

2 |

1 |

1 |

1 |

20 |

12.5 |

1250 |

312.5 |

PASS |

| 39 |

4 |

2 |

1 |

1 |

0 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 40 |

4 |

2 |

1 |

1 |

1 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 41 |

4 |

2 |

2 |

1 |

0 |

16 |

12.5 |

1250 |

312.5 |

PASS |

| 42 |

4 |

2 |

2 |

1 |

1 |

16 |

12.5 |

1250 |

312.5 |

PASS |

| 43 |

4 |

2 |

2 |

1 |

0 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 44 |

4 |

2 |

2 |

1 |

1 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 45 |

8 |

2 |

1 |

1 |

0 |

20 |

6.25 |

1250 |

156.25 |

PASS |

| 46 |

8 |

2 |

1 |

1 |

1 |

20 |

6.25 |

1250 |

156.25 |

PASS |

| 47 |

8 |

2 |

1 |

1 |

0 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 48 |

8 |

2 |

1 |

1 |

1 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 49 |

8 |

2 |

2 |

1 |

0 |

16 |

6.25 |

1250 |

156.25 |

PASS |

| 50 |

8 |

2 |

2 |

1 |

1 |

16 |

6.25 |

1250 |

156.25 |

PASS |

| 51 |

8 |

2 |

2 |

1 |

0 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 52 |

8 |

2 |

2 |

1 |

1 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 53 |

1 |

4 |

8 |

1 |

0 |

16 |

12.5 |

312.5 |

312.5 |

PASS |

| 54 |

1 |

4 |

8 |

1 |

1 |

16 |

12.5 |

312.5 |

312.5 |

PASS |

| 55 |

1 |

4 |

8 |

1 |

0 |

32 |

12.5 |

312.5 |

312.5 |

PASS |

| 56 |

1 |

4 |

8 |

1 |

1 |

32 |

12.5 |

312.5 |

312.5 |

PASS |

| 57 |

2 |

4 |

4 |

1 |

0 |

16 |

12.5 |

625 |

312.5 |

PASS |

| 58 |

2 |

4 |

4 |

1 |

1 |

16 |

12.5 |

625 |

312.5 |

PASS |

| 59 |

2 |

4 |

4 |

1 |

0 |

32 |

12.5 |

625 |

312.5 |

PASS |

| 60 |

2 |

4 |

4 |

1 |

1 |

32 |

12.5 |

625 |

312.5 |

PASS |

| 61 |

4 |

4 |

2 |

1 |

0 |

16 |

12.5 |

1250 |

312.5 |

PASS |

| 62 |

4 |

4 |

2 |

1 |

1 |

16 |

12.5 |

1250 |

312.5 |

PASS |

| 63 |

4 |

4 |

2 |

1 |

0 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 64 |

4 |

4 |

2 |

1 |

1 |

32 |

12.5 |

1250 |

312.5 |

PASS |

| 65 |

8 |

4 |

1 |

1 |

0 |

20 |

6.25 |

1250 |

156.25 |

PASS |

| 66 |

8 |

4 |

1 |

1 |

1 |

20 |

6.25 |

1250 |

156.25 |

PASS |

| 67 |

8 |

4 |

1 |

1 |

0 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 68 |

8 |

4 |

1 |

1 |

1 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 69 |

8 |

4 |

2 |

1 |

0 |

16 |

6.25 |

1250 |

156.25 |

PASS |

| 70 |

8 |

4 |

2 |

1 |

1 |

16 |

6.25 |

1250 |

156.25 |

PASS |

| 71 |

8 |

4 |

2 |

1 |

0 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 72 |

8 |

4 |

2 |

1 |

1 |

32 |

6.25 |

1250 |

156.25 |

PASS |

| 73 |

2 |

8 |

8 |

1 |

0 |

16 |

12.5 |

312.5 |

312.5 |

PASS with comments |

| 74 |

2 |

8 |

8 |

1 |

1 |

16 |

12.5 |

312.5 |

312.5 |

PASS with comments |

| 75 |

2 |

8 |

8 |

1 |

0 |

32 |

12.5 |

312.5 |

312.5 |

PASS with comments |

| 76 |

2 |

8 |

8 |

1 |

1 |

32 |

12.5 |

312.5 |

312.5 |

PASS with comments |

| 77 |

4 |

8 |

4 |

1 |

0 |

16 |

12.5 |

625 |

312.5 |

PASS with comments |

| 78 |

4 |

8 |

4 |

1 |

1 |

16 |

12.5 |

625 |

312.5 |

PASS with comments |

| 79 |

4 |

8 |

4 |

1 |

0 |

32 |

12.5 |

625 |

312.5 |

PASS with comments |

| 80 |

4 |

8 |

4 |

1 |

1 |

32 |

12.5 |

625 |

312.5 |

PASS with comments |

| 81 |

8 |

8 |

2 |

1 |

0 |

16 |

12.5 |

1250 |

312.5 |

PASS with comments |

| 82 |

8 |

8 |

2 |

1 |

1 |

16 |

12.5 |

1250 |

312.5 |

PASS with comments |

| 83 |

8 |

8 |

2 |

1 |

0 |

32 |

12.5 |

1250 |

312.5 |

PASS with comments |

| 84 |

8 |

8 |

2 |

1 |

1 |

32 |

12.5 |

1250 |

312.5 |

PASS with comments |

The following table shows the results for test cases DL.1, DL.2, DL.3 and DL.4 with different values of L, M, F, K, subclass, data rate, sampling clock, link clock and SYSREF frequencies.

| Test |

L |

M |

F |

Subclass |

K |

Data rate (Gbps) |

Sampling Clock (MHz) |

Link Clock (MHz) |

Result |

Latency (Link Clock Cycles) |

|---|---|---|---|---|---|---|---|---|---|---|

| DL.1 |

1 |

1 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

For K=16 DL= 75 For K=32 DL= 115 |

| DL.2 |

1 |

1 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.3 |

1 |

1 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.4 |

1 |

1 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.1 |

2 |

1 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

For K=20 DL= 53 For K=32 DL= 67 |

| DL.2 |

2 |

1 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.3 |

2 |

1 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.4 |

2 |

1 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.1 |

2 |

1 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

For K=16 DL=67 For K=32 DL=99 |

| DL.2 |

2 |

1 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.3 |

2 |

1 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.4 |

2 |

1 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.1 |

4 |

1 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

For K=20 DL=53 For K=32 DL=67 |

| DL.2 |

4 |

1 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.3 |

4 |

1 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.4 |

4 |

1 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.1 |

4 |

1 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

For K=16 DL=67 For K=32 DL=99 |

| DL.2 |

4 |

1 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.3 |

4 |

1 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.4 |

4 |

1 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.1 |

8 |

1 |

1 |

1 |

20/32 |

3.125 |

1250 |

78.125 |

PASS |

For K=20 DL=53 For K=32 DL=67 |

| DL.2 |

8 |

1 |

1 |

1 |

20/32 |

3.125 |

1250 |

78.125 |

PASS |

|

| DL.3 |

8 |

1 |

1 |

1 |

20/32 |

3.125 |

1250 |

78.125 |

PASS |

|

| DL.4 |

8 |

1 |

1 |

1 |

20/32 |

3.125 |

1250 |

78.125 |

PASS |

|

| DL.1 |

8 |

1 |

2 |

1 |

16/32 |

3.125 |

1250 |

78.125 |

PASS |

For K=16 DL=67 For K=32 DL=115 |

| DL.2 |

8 |

1 |

2 |

1 |

16/32 |

3.125 |

1250 |

78.125 |

PASS |

|

| DL.3 |

8 |

1 |

2 |

1 |

16/32 |

3.125 |

1250 |

78.125 |

PASS |

|

| DL.4 |

8 |

1 |

2 |

1 |

16/32 |

3.125 |

1250 |

78.125 |

PASS |

|

| DL.1 |

1 |

2 |

4 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

For K=16 DL=99 For K=32 DL=195 |

| DL.2 |

1 |

2 |

4 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.3 |

1 |

2 |

4 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.4 |

1 |

2 |

4 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.1 |

2 |

2 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

For K=16 DL=67 For K=32 DL=115 |

| DL.2 |

2 |

2 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.3 |

2 |

2 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.4 |

2 |

2 |

2 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.1 |

4 |

2 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

For K=20 DL=56 For K=32 DL=67 |

| DL.2 |

4 |

2 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.3 |

4 |

2 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.4 |

4 |

2 |

1 |

1 |

20/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.1 |

4 |

2 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

For K=16 DL=67 For K=32 DL=99 |

| DL.2 |

4 |

2 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.3 |

4 |

2 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.4 |

4 |

2 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.1 |

8 |

2 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

For K=20 DL=52 For K=32 DL=67 |

| DL.2 |

8 |

2 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.3 |

8 |

2 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.4 |

8 |

2 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.1 |

8 |

2 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

For K=16 DL=67 For K=32 DL=99 |

| DL.2 |

8 |

2 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.3 |

8 |

2 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.4 |

8 |

2 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.1 |

1 |

4 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

For K=16 DL=195 For K=32 DL=67 |

| DL.2 |

1 |

4 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.3 |

1 |

4 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.4 |

1 |

4 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.1 |

2 |

4 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

For K=16 DL=115 For K=32 DL=195 |

| DL.2 |

2 |

4 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.3 |

2 |

4 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.4 |

2 |

4 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.1 |

4 |

4 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

For K=16 DL=67 For K=32 DL=99 |

| DL.2 |

4 |

4 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.3 |

4 |

4 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.4 |

4 |

4 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.1 |

8 |

4 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

For K=20 DL=51 For K=32 DL=67 |

| DL.2 |

8 |

4 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.3 |

8 |

4 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.4 |

8 |

4 |

1 |

1 |

20/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.1 |

8 |

4 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

For K=16 DL=67 For K=32 DL=99 |

| DL.2 |

8 |

4 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.3 |

8 |

4 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.4 |

8 |

4 |

2 |

1 |

16/32 |

6.25 |

1250 |

156.25 |

PASS |

|

| DL.1 |

2 |

8 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

For K=16 DL=195 For K=32 DL=67 |

| DL.2 |

2 |

8 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.3 |

2 |

8 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS |

|

| DL.4 |

2 |

8 |

8 |

1 |

16/32 |

12.5 |

312.5 |

312.5 |

PASS with comments |

|

| DL.1 |

4 |

8 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

For K=16 DL=115 For K=32 DL=195 |

| DL.2 |

4 |

8 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.3 |

4 |

8 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS |

|

| DL.4 |

4 |

8 |

4 |

1 |

16/32 |

12.5 |

625 |

312.5 |

PASS with comments |

|

| DL.1 |

8 |

8 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

For K=16 DL=67 For K=32 DL=99 |

| DL.2 |

8 |

8 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.3 |

8 |

8 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS |

|

| DL.4 |

8 |

8 |

2 |

1 |

16/32 |

12.5 |

1250 |

312.5 |

PASS with comments |

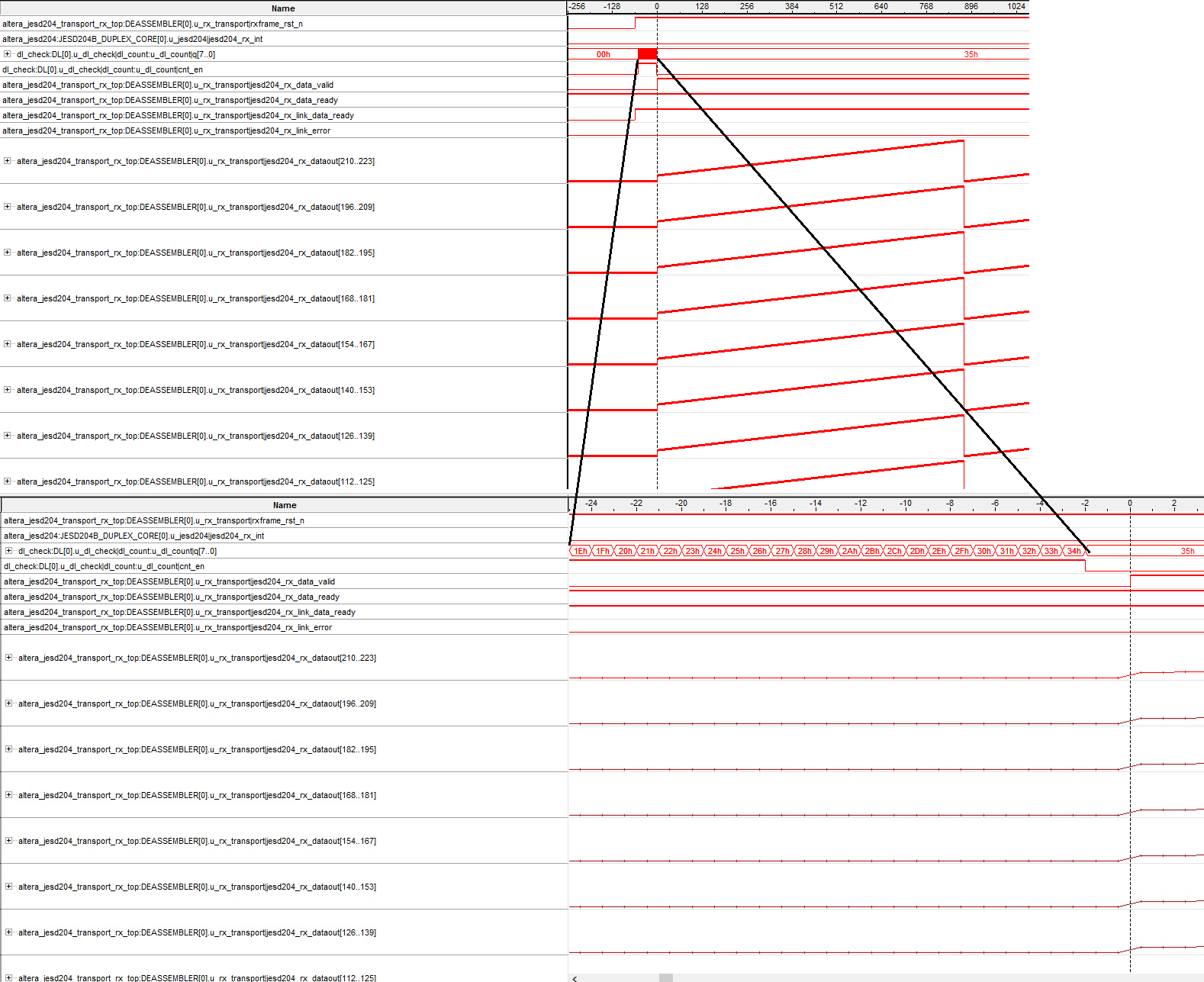

The following figure shows the Signal Tap waveform of the clock count from the deassertion of SYNC~ to the assertion of the jesd204_rx_link_valid signal, the first output of the ramp test pattern (DL.3 test case). The clock count measures the first user data output latency.