Multi Channel DMA IP for PCI Express* Design Example User Guide

ID

683517

Date

8/04/2025

Public

3.5.1. Hardware Requirements

3.5.2. Software Requirements

3.5.3. Set Up the Hardware and Program the FPGA

3.5.4. Configuration Changes from BIOS

3.5.5. Installing the Required Kernel Version for Ubuntu v24.04

3.5.6. Set the Boot Parameters

3.5.7. MCDMA Custom Driver

3.5.8. MCDMA DPDK Poll Mode Driver

3.5.9. MCDMA Kernel Mode Network Device Driver

3.3.1. Testbench Overview

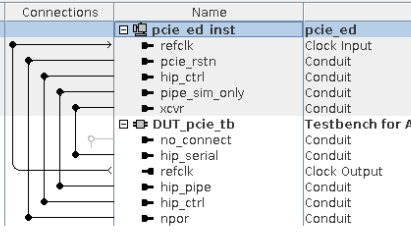

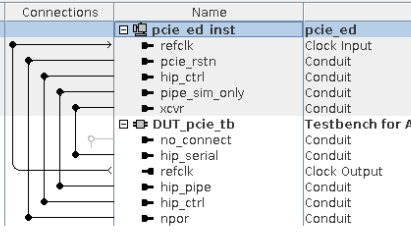

Figure 27. Testbench Platform Designer View

The design example, pcie_ed_inst, is generated with the link width you select in the IP Parameter Editor. The FPGA BFM, DUT_pcie_tb, is a Root Port BFM.

Note: The H-Tile Root Port BFM only supports up to Gen3 x8 width and downtrains x16 Endpoint to Gen3 x8. If you want to simulate x16 link width with MCMDA H-Tile Endpoint, you can use a third-party Root Complex BFM.

The testbench uses a Root Port driver module to initiate the configuration and exercise the target memory and DMA channel in the Endpoint. This is the module that you can modify to vary the transactions sent to the example Endpoint design or your own design.

The driver module path and file is as follows:

- MCDMA R-Tile testbench

Path: pcie_ed_sim_tb/ip/pcie_ed_sim_tb/dut_pcie_tb_ip/intel_pcie_rtile_tbed_100/sim

File: altpcietb_bfm_rp_gen5_x16.sv

- MCDMA P-Tile testbench

Path: pcie_ed_sim_tb/ip/pcie_ed_sim_tb/DUT_pcie_tb_ip/intel_pcie_ptile_tbed_100/sim

File: altpcietb_bfm_rp_gen4_x16.sv

- MCDMA F-Tile testbench

Path: pcie_ed_sim_tb/ip/pcie_ed_sim_tb/dut_pcie_tb_ip/intel_pcie_ftile_tbed_100/sim

File: altpcietb_bfm_rp_gen4_x16.sv

- MCDMA H-Tile testbench

Path: pcie_ed_sim_tb/ip/pcie_ed_sim_tb/DUT_pcie_tb_ip/altera_pcie_s10_tbed_191/sim

File: altpcietb_bfm_rp_gen3_x8.sv

For more information about the FPGA BFM, refer to the Testbench overview in the user guides provided below:

- P-Tile Avalon® Streaming FPGA IP for PCI Express* User Guide

- F-Tile Avalon® Streaming FPGA IP for PCI Express* User Guide

- R-Tile Avalon Streaming FPGA IP for PCI Express Design Example User Guide

- L- and H-tile Avalon® Streaming and Single Root I/O Virtualization (SR-IOV) FPGA IP for PCI Express* User Guide