Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

11/04/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.2.5.1. Build and Install Netdev Driver

3.5.2.5.2. Enable VFs if SRIOV is Supported

3.5.2.5.3. Configure the Number of Channels Supported on the Device

3.5.2.5.4. Configure the MTU Value

3.5.2.5.5. Configure the Device Communication

3.5.2.5.6. Configure Transmit Queue Selection Mechanism

3.5.2.5.7. Test Procedure by Using Name Space Environment

3.5.2.5.8. PIO Test

2.3.2.1. Simulation Results

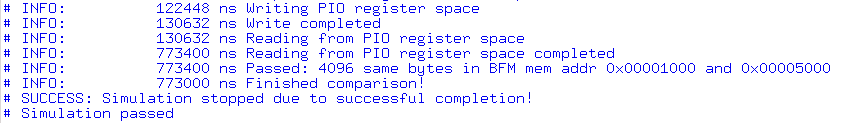

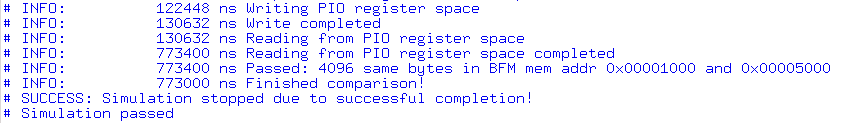

Testbench writes 4 KB of incrementing pattern to on-chip memory and read back via Avalon-MM PIO interface. This design example testbench doesn’t simulate H2D/D2H data movers.

Figure 3. Simulation Log

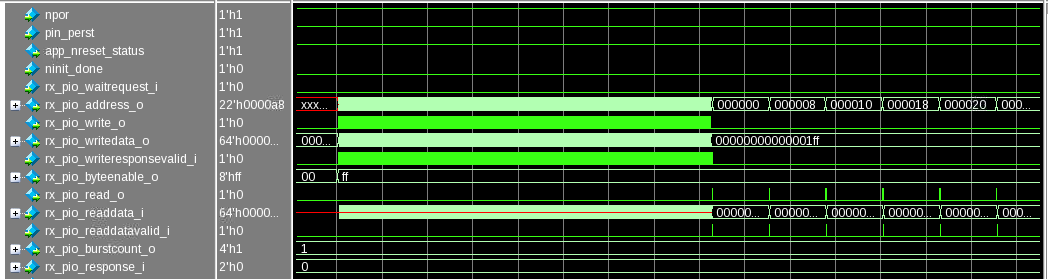

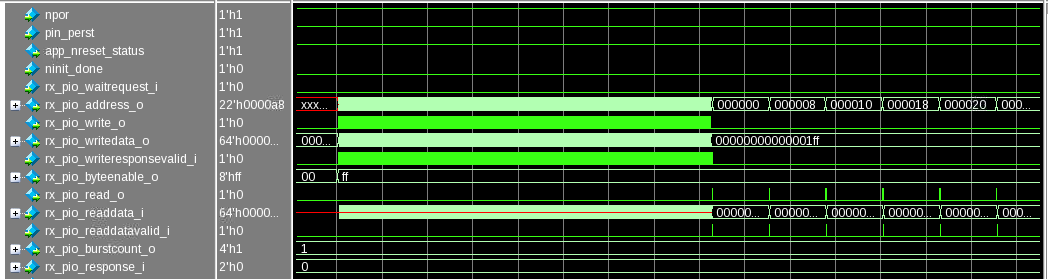

Figure 4. Simulation Waveform