Intel® Arria® 10 and Intel® Cyclone® 10 Avalon® Memory-mapped Interface for PCIe* Design Example User Guide

1.4. Simulating the Design

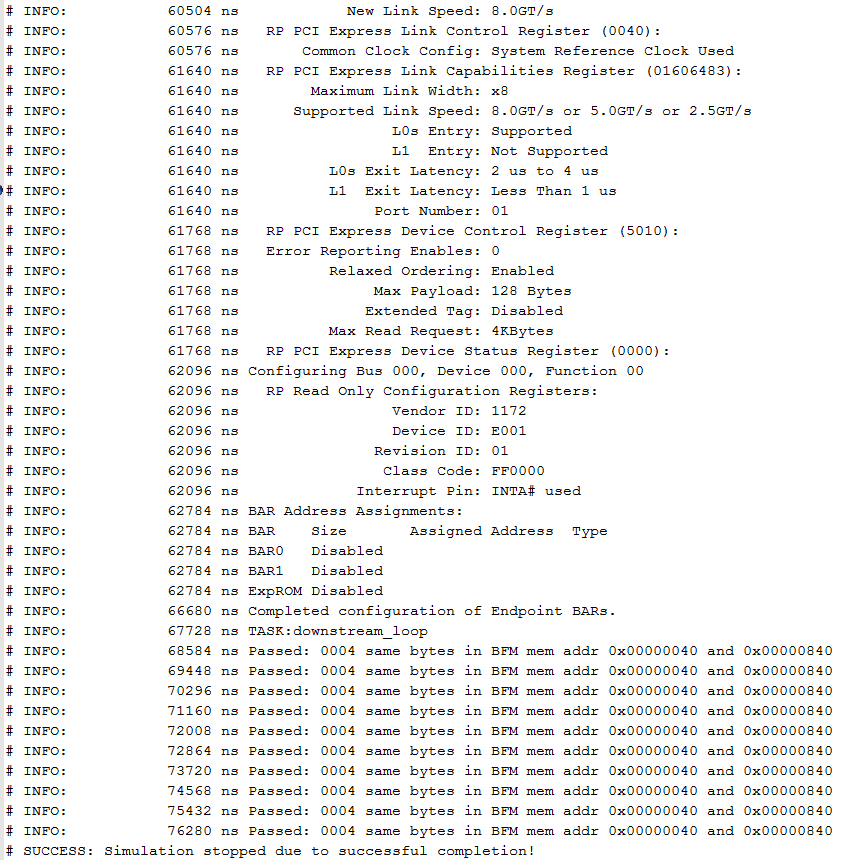

Figure 4. Procedure

- Change to the testbench simulation directory.

- Run the simulation script for the simulator of your choice. Refer to the table below.

- Analyze the results.

| Simulator | Working Directory | Instructions |

|---|---|---|

| ModelSim* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/mentor/ |

|

| VCS* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/synopsys/vcs |

|

| NCSim* | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/cadence |

|

| Xcelium* Parallel Simulator | <example_design>/pcie_example_design_tb/pcie_example_design_tb/sim/xcelium |

|

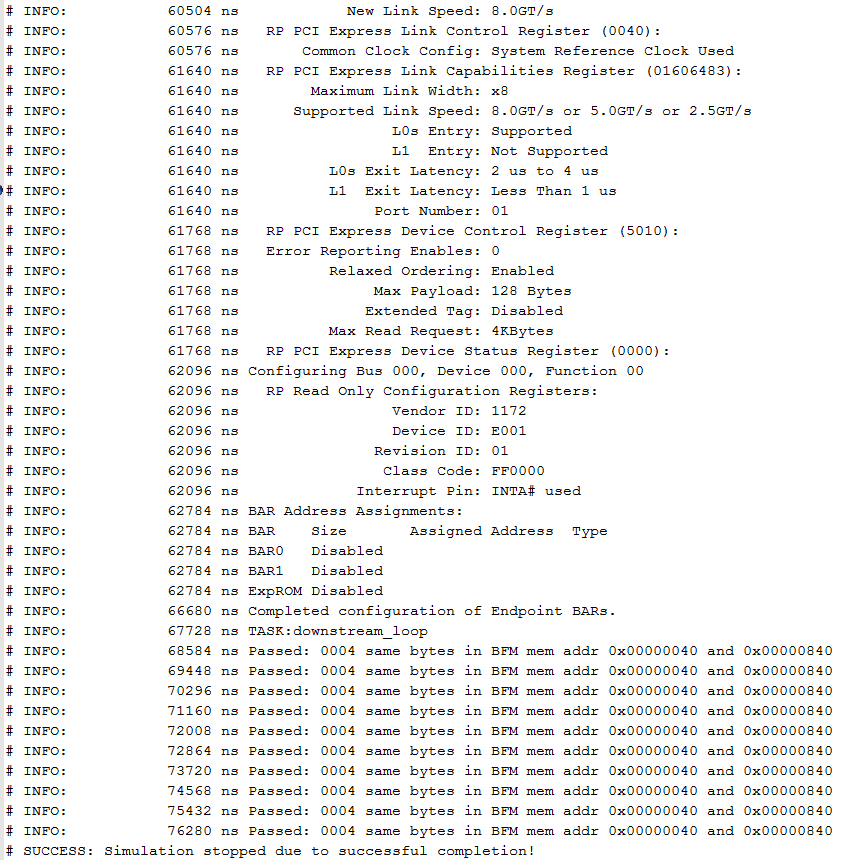

Figure 5. Partial Transcript from Successful Endpoint Avalon-ST PIO Simulation Testbench