E-Tile Hard IP User Guide: E-Tile Hard IP for Ethernet and E-Tile CPRI PHY Intel® FPGA IPs

3.7.4. E-Tile CPRI PHY Intel FPGA IP Channel Placement

Each E-tile offers up to 24 fractured mode channels. For E-Tile CPRI PHY IP, each E-tile provides up to 23 channels since the 24th channel has to be configured in PLL mode to provide 403 MHz/806 MHz clock to other CPRI channels.

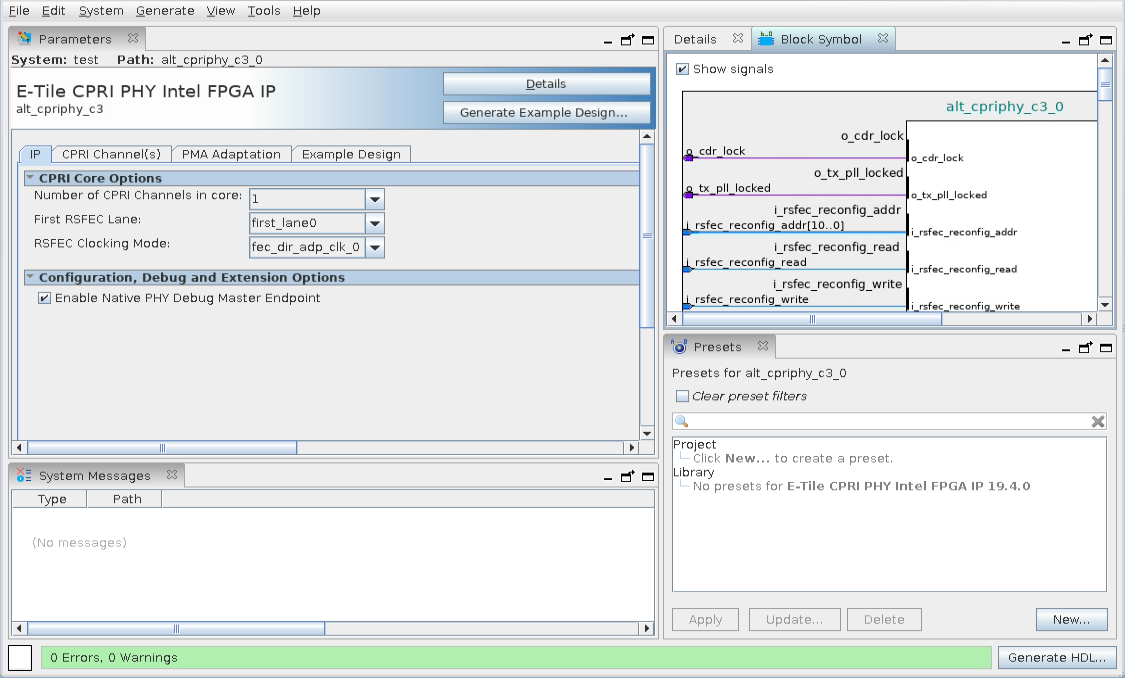

The section below explains how the First RSFEC Lane and RSFEC Clocking Mode parameter works for the E-Tile CPRI PHY IP.

The following figure shows one master 24 Gbps channel providing the datapath clock to other three slave 24 Gbps channels.

The E-Tile CPRI PHY IP uses Native PHY in PLL mode to provide 402.83 MHz and 805.66 MHz clock. All CPRI data rates use the Native PHY in PLL mode. For more information on how to implement the native PHY in PLL mode, refer to the PLL Mode section of E-Tile Transceiver PHY User Guide.

As shown in the figure below, the E-tile CPRI PHY uses Ethernet's clock frequencies because the Ethernet to CPRI dynamic reconfiguration uses Ethernet as the power up protocol so that AIB clock is fixed at Ethernet line rate and it remains unchanged after reconfiguration to CPRI line rates.

All four channels use a common RS-FEC block. However, the RS-FEC block uses only one clock from the available four channels. The channel that provides the FEC clock works as a master. The other three channels that uses the same clock for clocking their TX and RX data path works as slave channels. This creates a dependency between the master and the slave channels.

When you implement one or multiple high speed CPRI data rates with RS-FEC channels, you select the first RS-FEC lane option. You have the flexibility to select which first lane to be your master channel.