F-Tile Avalon® Streaming Intel® FPGA IP for PCI Express* Design Example User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

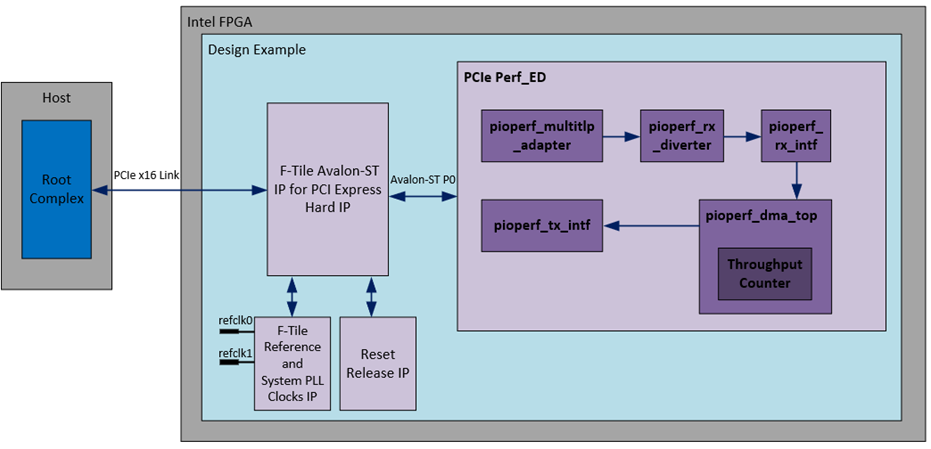

2.3. Performance Design Example

The Performance Design Example is designed to showcase the performance of the F-Tile Avalon-ST for PCI Express Hard IP. It can be configured to send memory write only TLPs, memory read-only TLPs or both memory write and memory read TLPs for throughput measurement. The throughput counter is implemented in the FPGA application logic to minimize the software overhead. For throughput measurement, the software application running at the host side issues a memory read TLP and acquires the throughput counter value from the control register and then prints the throughput figure at the system terminal. The software application is required to issue a memory write to the control register to stop the traffic at the end of the test.

The Performance Design Example automatically creates the files necessary to simulate and compile in the Intel® Quartus® Prime software. It supports the Gen4 x16, 512-bit interface Hard IP mode. For the Intel® Agilex™ device family, this design example supports up to a 500 MHz PLD clock frequency.