Quartus® Prime Pro Edition User Guide: Design Compilation

ID

683236

Date

9/29/2025

Public

1.1. Compilation Overview

1.2. Design Analysis & Elaboration

1.3. Design Synthesis

1.4. Design Place and Route

1.5. Incremental Optimization Flow

1.6. Fast Forward Compilation Flow

1.7. Full Compilation Flow

1.8. HSSI Dual Simplex IP Generation Flow

1.9. Exporting Compilation Results

1.10. Clearing Compilation Results

1.11. Integrating Other EDA Tools

1.12. Compiler Optimization Techniques

1.13. Compilation Monitoring Mode

1.14. Viewing Quartus Database File Information

1.15. Understanding the Design Netlist Infrastructure

1.16. Using Synopsys* Design Constraint (SDC) on RTL Files

1.17. Using the Node Finder

1.18. Synthesis Language Support

1.19. Synthesis Settings Reference

1.20. Fitter Settings Reference

1.21. Design Compilation Revision History

2.1. Factors Affecting Compilation Results

2.2. Strategies to Reduce the Overall Compilation Time

2.3. Reducing Synthesis Time

2.4. Reducing Placement Time

2.5. Reducing Routing Time

2.6. Reducing Static Timing Analysis Time

2.7. Setting Process Priority

2.8. Reducing Compilation Time Revision History

1.2. Design Analysis & Elaboration

The Analysis & Elaboration stage provides a complete and unmodified view of your design early in the compilation flow. Analysis & Elaboration generates an initial design netlist for analysis. Analysis & Elaboration is the first stage of design synthesis. If enabled, Precompiled Component Generation partially synthesizes IP components in your design, and stores the compilation results in a project subdirectory called IP cache during Analysis & Elaboration, as Using Precompiled Component Generation describes.

Figure 3. Analysis & Elaboration Checkpoints

The Analysis & Elaboration stage comprises a series of checkpoints. You can preview your design results at each checkpoint as shown in Analysis & Elaboration Checkpoints, where:

- Elaborated: Provides an unmodified preview of your design captured directly from RTL.

- Instrumented: Provides an instrumented preview with system-level debugging (debug fabric and Signal Tap logic analyzer inserted in your design). This checkpoint is disabled by default (Hint: See Note below to enable it).

- Constrained: Provides a design preview with SDC-on-RTL constraints shown on the target nodes. This checkpoint is disabled by default (Hint: See Note below to enable it).

- Swept: Provides a design preview with unnecessary logic removed from your design.

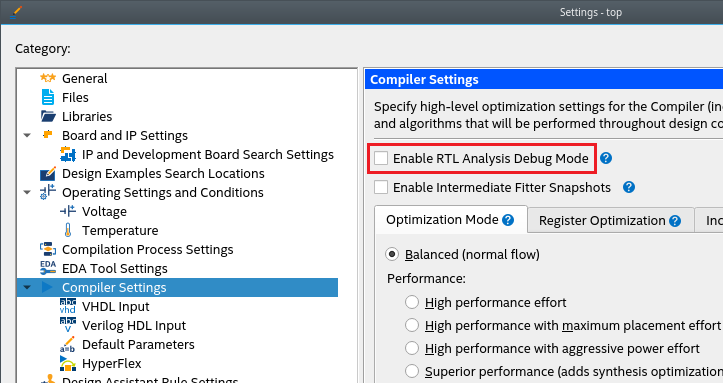

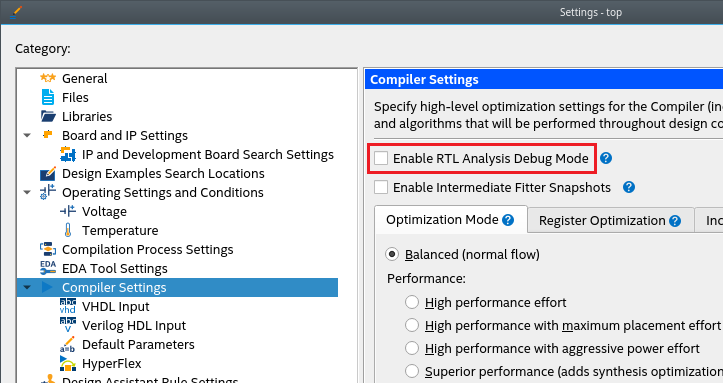

You can control the number of checkpoints generated using the RTL Analysis Debug Mode option under Project > Settings. This mode is off by default, which means only Elaborated and Swept checkpoints are available, and Instrumented and Constrained checkpoints are unavailable. When you enable this mode, all four checkpoints become available.

When the mode is off, you can obtain information about the Hierarchies Optimized Away and Top Causes for Logic Optimized Away During Sweep, under Synthesis Compilation Reports > Synthesis > Analysis & Elaboration.

Figure 4. Compiler Settings