Quartus® Prime Pro Edition User Guide: Design Compilation

1.2.2. Analyzing Design RTL

After running the Compiler's Design Analysis 1 or Analysis & Elaboration stage, you can visualize and analyze your design RTL in the RTL Analyzer. The RTL Analyzer provides a graphical display the unmodified design RTL captured directly from you HDL source files.

You can use this RTL Analyzer to visualize the hierarchy and to help specify any SDC-on-RTL constraints prior to synthesis.

To run the RTL Analyzer:

- In the Compilation Dashboard, Run the Compiler's Design Analysis or Analysis & Elaboration stage.

- Click the RTL Analyzer icon for the Design Analysis or Analysis & Elaboration stage.

Figure 6. Open RTL Analyzer Icon (Magnified) in Compilation Dashboard

The RTL Analyzer provides the following to help you visualize the design RTL information:

- Netlist Navigator—browse a clickable list of the core elements of your design RTL hierarchy, including modules, instances, ports, instance ports, and nets.

- Schematic Viewer—clickable schematic representation of the core elements of your design RTL hierarchy, including modules, instances, ports, instance ports, and nets.

- Object Property Viewer—displays the detailed properties of core elements that you select in RTL Analyzer.

Use Netlist Navigator to Browse Design Hierarchy

The Netlist Navigator allows you to quickly browse the elements of the design netlist five-box data model. The core elements of this data model are modules, instances, ports, instance ports, and nets. For more information about this data model, refer to DNI Netlist Five-Box Data Model.

All objects in the hierarchy are organized in the Netlist Navigator by the object type. For example, I/Os are grouped based on the direction.

Various GUI elements of the RTL analyzer synchronize with the objects in the Objects pane. For example, when you select an object in the Netlist Navigator, the object highlights in the Schematic Viewer, and the Tcl Consoledisplays the equivalent Tcl command. Correspondingly, the Properties viewer provides relevant information about the selected object.

You can cross-probe from selected objects in the netlist to the source definition by right-clicking on an object and selecting Locate Node > Locate in Design File. The source file displays in the Quartus® Prime Text Editor.

Schematic Viewer

The Schematic Viewer displays a schematic representation of the design elements in the netlist, such as modules, instances, ports, instance ports, and nets. The viewer updates dynamically as you select elements in the Netlist Navigator to shift focus to the current element as you navigate through the netlist.

Properties Viewer

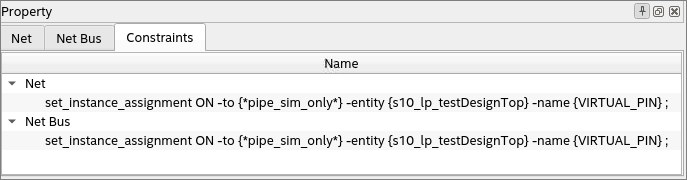

The Property pane provides information about assignments and SDC constraints attached to the selected object in the hierarchy browser. You can cross-probe to the definition of the assignment in the source file.

Tcl Console

The Tcl Console provides a robust scripting interface that reports issues and displays relevant Tcl commands for GUI actions. It allows you to traverse and analyze your design. As you type the Tcl commands, notice how the schematic viewer and the hierarchy browser respond accordingly.

Object Finder

The object finder helps in locating an object in the design netlist. You can refine your search based on the object type (instance, instance bus, inst_port, port, port_bus, net, and net_bus) and modules. For complicated designs, you can further use filters to refine your search.

The RTL Analyzer provides the following tools and functionality:

- Sweep Hints Viewer

Object Set Console

Module Interfaces

Bundled Instances

Auto-hide Unconnected Pins

Filtering Ports and Nets

Expand Connections