4.8.1. Deterministic Latency Top Wrapper

- TX DL shim wrapper

- RX DL shim wrapper

- F-Tile Serial Lite IV Intel® FPGA IP

SYSREF Pulse Generator is available in the example design. Refer to the F-Tile Serial Lite IV Intel® FPGA IP Design Example User Guide for more information.

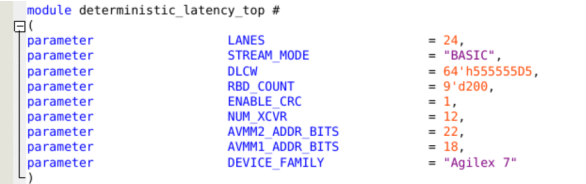

The DLCW (Deterministic Latency Control Word) pattern is preset to 555555D5 per lane in the design module. The RBD_COUNT parameter value is preset to 9 ’d200. You can set the RBD_COUNT parameter value to another targeted value.

| Signal Name | Direction | Type | Description |

|---|---|---|---|

| tx_user_clock | input | wire | Input clock from user clock source. |

| tx_core_clkout | input | wire | Input clock source from F-Tile Serial Lite IV Intel® FPGA IP core tx_core_clk. |

| tx_user_clock_reset | input | wire | Active high async reset. Assert the reset when F-Tile Serial Lite IV Intel® FPGA IP core tx_core_rst is asserted. |

| sysref | input | wire | Periodic pulse signal from SYSREF generator |

| rxinsync_tx_in | input | wire | Input signal from RX DL wrapper to indicate DLCW word has been received on all the lanes and the data has been passed to the Rx Proc logic |

| tx_link_up | output | wire | Tx link up signal from F-Tile Serial Lite IV Intel® FPGA IP core. |

| tx_data | input | wire [(N*2*64)-1:0] | Avalon® streaming interface Data signal from user traffic generator. |

| tx_valid | input | wire [(N*2)-1:0] | Avalon® streaming interface Valid signal from user traffic generator. |

| tx_ready | output | wire | Avalon® streaming interface Ready signal from F-Tile Serial Lite IV Intel® FPGA IP core. |

| tx_error | output | wire [4:0] | Unused |

| tx_user_data_sel | output | wire | Output signal connected to user traffic generator to indicate that it is ready to receive user data. |

| tx_dl_fifo_pfull | output | wire [(N*2)-1:0] | Output status signal to indicate the internal FIFO under partial full status |

| tx_dl_fifo_full | output | wire [(N*2)-1:0] | Output status signal to indicate the internal FIFO under full status |

| rx_user_clock | input | wire | Input clock from user clock source |

| rx_core_clkout | input | wire | Input clock from F-Tile Serial Lite IV Intel® FPGA IP rx_core_clk |

| rxinsync_rx_out | output | wire | Indicates DLCW word has been received on all the lanes and the data has been passed to the Rx Proc logic |

| dl_sync_up | output | wire | Indicates DL synchronization process is successful |

| rx_data_in | output | wire [(N*2*64)-1:0] | Avalon® streaming interface Data to user traffic checker |

| rx_ valid_in | output | wire | Avalon® streaming interface Valid to user traffic checker |

| rx_valid | input | wire | Avalon® streaming interface Valid signal from F-Tile Serial Lite IV Intel® FPGA IP core |

| rx_ error | output | wire [((N*2)+3]-1:0] | Indicates the error condition of the F-Tile Serial Lite IV Intel® FPGA IP RX path |

| rx_dl_fifo_empty | output | wire | Output status signal to indicate the internal FIFO hits empty status |

| rx_dl_fifo_full | output | wire | Output status signal to indicate the internal FIFO hits full status |

| rx_link_up | output | wire | Rx link up signal from F-Tile Serial Lite IV Intel® FPGA IP core. |

| rx_ready | input | wire | Avalon® streaming interface Ready signal to F-Tile Serial Lite IV Intel® FPGA IP core. |

| tx_core_rst_n | input | wire | Resetting the SRL4 TX_CORE, active LOW, ASYNC |

| rx_core_rst_n | input | wire | Resetting the SRL4 RX_CORE, active LOW, ASYNC |

The remaining signals are Serial Lite IV IP specific. Refer to F-Tile Serial Lite IV Intel FPGA IP Interface Signals for details.

Reset signals: tx_pcs_fec_phy_reset_n, rx_pcs_fec_phy_reset_n, tx_reset_ack, rx_reset_ack.

MAC signals: tx_link_reinit, rx_link_reinit, crc_error_inject.

PMA signals: tx_pll_locked, phy_tx_lanes_stable, phy_ehip_ready, phy_rx_pcs_ready, phy_rx_hi_ber, phy_rx_block_lock, rx_cdr_lock, tx_serial_data, rx_serial_data, tx_serial_data_n, rx_serial_data_n.

Transceiver Reconfig signals: reconfig_*, reconfig_sl_*, i_stats_snapshot.