1.1. Generating Primary Device Programming Files

1.2. Generating Secondary Programming Files

1.3. Enabling Bitstream Security for Stratix® 10 and Agilex™ 7 Devices

1.4. Enabling Bitstream Encryption or Compression for Arria® 10 and Cyclone® 10 GX Devices

1.5. Generating Programming Files for Partial Reconfiguration

1.6. Generating Programming Files for Altera® FPGA Devices with Hard Processor Systems

1.7. Scripting Support

1.8. Generating Programming Files Revision History

2.1. Quartus® Prime Programmer

2.2. Programming and Configuration Modes

2.3. Basic Device Configuration Steps

2.4. Specifying the Programming Hardware Setup

2.5. Programming with Flash Loaders

2.6. Verifying the Programming File Source with Project Hash

2.7. Using PR Bitstream Security Verification ( Stratix® 10 Designs)

2.8. Stand-Alone Programmer and Tools

2.9. Programmer Settings Reference

2.10. Scripting Support

2.11. Using the Quartus® Prime Programmer Revision History

2.9.1. Device & Pin Options Dialog Box

2.9.2. More Security Options Dialog Box

2.9.3. Output Files Tab Settings (Programming File Generator)

2.9.4. Input Files Tab Settings (Programming File Generator)

2.9.5. Bitstream Co-Signing Security Settings (Programming File Generator)

2.9.6. Configuration Device Tab Settings

2.9.7. Add Partition Dialog Box (Programming File Generator)

2.9.8. Add Filesystem Dialog Box (Programming File Generator)

2.9.9. Convert Programming File Dialog Box

2.9.10. Compression and Encryption Settings (Convert Programming File)

2.9.11. SOF Data Properties Dialog Box (Convert Programming File)

2.9.12. Select Devices (Flash Loader) Dialog Box

1.6.2. Generating Programming Files for FPGA Configuration First Boot Flows

In FPGA Configuration First boot flows, the FPGA core and periphery are configured first. After that, the HPS can optionally be booted.

To generate programming files for FPGA Configuration First boot flows

- Generate the primary programming files for your design, as Generating Primary Device Programming Files describes.

- Click File > Programming File Generator.

- For Device family, select your target device. The options available in the Programming File Generator change dynamically, according to your device and configuration mode selection.

- For Configuration mode, select an Active Serial mode that your device supports. Configuration Modes (Programming File Generator) describes all modes.

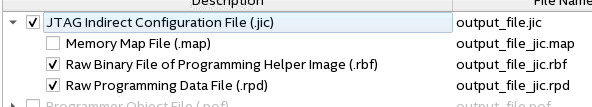

- On the Output Files tab, select JTAG Indirect Configuration File (.jic), then select the following files:

Raw Binary File of Programming Helper Image (.rbf)

Raw Programming Data File (.rpd)

Secondary Programming Files (Programming File Generator) describes all output files.

- On the Output Files tab, select Raw Programming Data File (.rpd) and click Edit.

- Optional: Optional: In the RPD Properties dialog box, set Bit swap to On.

Important: This step may or may not be required, depending on the external programmer that you use.

- Specify the Output directory and Name for the file you generate. Output Files Tab Settings (Programming File Generator) describes all options.

- On the Input Files tab, click Add Bitstream to add your .sof file and then edit its properties:

- Select the .sof file and click Properties.

- In the Bootloader field of Input File Properties dialog box, add the U-Boot First State Boot Loader (FSBL) hex file (.hex).

- To add other data, such as a U-Boot Second Stage Boot Loader (SSBL) file or Phase 2 bitstreams:

- Click Add Raw Data and specify an Intel-format hexadecimal (.hex) file.

- Select the file you added and click Properties.

- In the Input File Properties dialog box, set the Bit swap field to On.

Important:Your Phase 1 and Phase 2 bitstreams are subject to the following restrictions:

- Your Phase 1 and Phase 2 bitstreams must be generated by the same version of Quartus® Prime, including any applied patches or updates.

- If your Phase 1 and Phase 2 bitstreams are generated from different Quartus® Prime Pro Edition projects, review the following Knowledge Base article for additional steps that might be required:

- To specify the .sof file that occupies the flash memory partition, click Add Partition on the Configuration Device tab. Add Partition Dialog Box (Programming File Generator) describes all options.

Figure 25. Add Flash Partition

- To select a supported flash memory device and predefined programming flow, click Add Device on the Configuration Device tab. Alternatively, click <<new device>> to define a new flash memory device and programming flow. Configuration Device Tab Settings describes all settings.

- Click the Select button for Flash Loader and select the device that controls loading of the flash memory device. Select Devices (Flash Loader) Dialog Box describes all settings.

- After you specify all options in Programming File Generator, the Generate button enables. Click Generate to create the files.

- Optional: Optional: Export your settings to a PFG setting file (.pfg) so that you can use these settings again with the quartus_pfg command line tool.

For details, refer to quartus_pfg Command Line Tool.

Related Information