Introduction

This design demonstrates the ECC Lite feature of the Nios® V/g core by injecting an error on

the General-Purpose Register (GPR) via simulation.

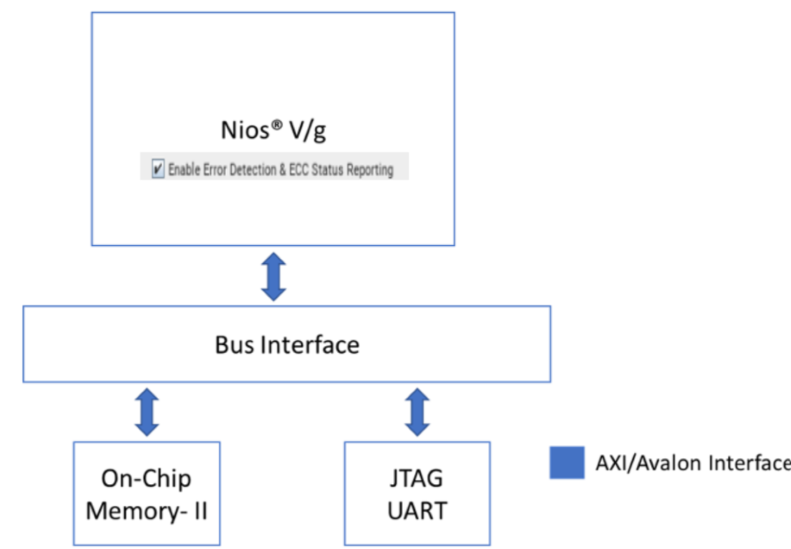

IP Cores

(0)

Detailed Description

This design demonstrates the ECC Lite feature of the Nios® V/g core by injecting an error on the General-Purpose Register (GPR) via simulation.

• The ECC status and ECC source is observed for both correctable and uncorrectable errors on the General-Purpose Registers (GPR).

• The Error is injected on the OCM (M20k) GPR through the ECC parity flip feature (Link).

• The parity value in the GPR is flipped using the force command in the test bench file (sys_tb.v). (Pg. 64 in Link)

• The ECC Status and ECC Source signals are probed and observed using Questa Simulation