Introduction

Development Kit

| IP Core | IP Core Category |

|---|---|

| Nios V/m Processor Intel FPGA IP | Embedded Processor |

| Generic Serial Flash Interface Intel FPGA IP | Configuration And Programming |

Detailed Description

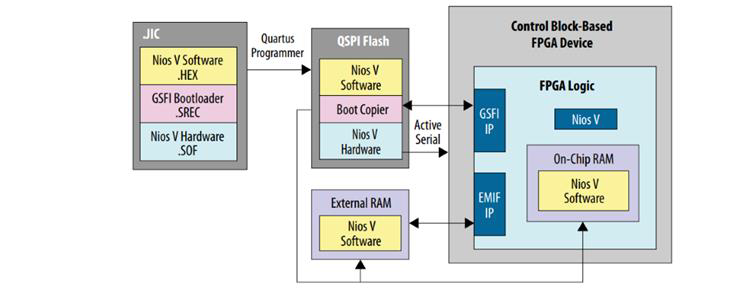

The GSFI bootloader is the Nios V processor boot copier that supports QSPI flash memory in control block-based devices.

The GSFI bootloader includes the following features:

- 1. Locates the software application in non-volatile memory.

- 2. Unpacks and copies the software application image to RAM.

- 3. Automatically switches processor execution to application code in RAM after copy completes.

Please refer to the document for details about the design.

Prepare the design template in the Quartus Prime software GUI

Note: After downloading the design example, you must prepare the design template. The file you downloaded is of the form of a <project>.par file which contains a compressed version of your design files (similar to a .qar file) and metadata describing the project. The combination of this information is what constitutes a <project>.par file. You can simply double click on the <project>.par file and Quartus will launch that project.