Introduction

Development Kit

| IP Core | IP Core Category |

|---|---|

| Nios V/m Processor Intel FPGA IP | Embedded Processor |

| Mailbox Client Intel FPGA IP | Configuration And Programming |

Detailed Description

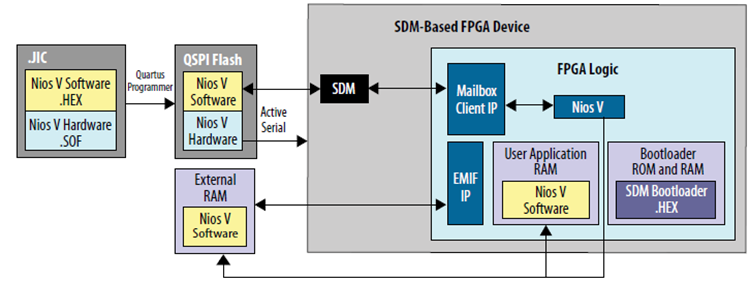

The Nios® V processor starts executing the boot copier upon system reset, which copies the application from the configuration quad serial peripheral interface (QSPI) to the internal RAM. Once this completes, the Nios V processor transfers the program control over to the application.

Please refer to the document for details about the design.

Prepare the design template in the Quartus Prime software GUI

Note: After downloading the design example, you must prepare the design template. The file you downloaded is of the form of a <project>.par file which contains a compressed version of your design files (similar to a .qar file) and metadata describing the project. The combination of this information is what constitutes a <project>.par file. You can simply double click on the <project>.par file and Quartus will launch that project.