Environment

Are Intel® Xeon® Processors Single‑Chip or Multi‑Chip Modules?

Summary

Intel® Xeon® processors may be built using either a single‑chip (monolithic) design or a multi‑chip module (MCM) design.

The architecture depends on the processor generation and model.

Both designs appear identical to software and operating systems, but they differ internally in how the silicon is packaged.

Intel® Xeon® Scalable Processors

4th Gen Intel® Xeon® Scalable Processors

- Architecture: Multi‑chip module (MCM)

- These processors use multiple internal compute tiles connected within a single package.

- This approach enables higher scalability and integrated accelerators.

5th Gen Intel® Xeon® Scalable Processors

- Architecture depends on the model:

- Low and Medium Core Count models: Single‑chip (monolithic)

- Extreme Core Count models: Multi‑chip module (MCM)

- This allows Intel to optimize for both performance efficiency and higher core density.

Intel® Xeon® 6 Processor Family

Starting with Intel® Xeon® 6, Intel transitioned fully to a modular, tile‑based architecture across the family.

Intel® Xeon® 6 with P‑cores

- Architecture: Multi‑chip module

- Uses multiple compute and I/O tiles in one processor package

- Designed for performance‑focused enterprise, AI, and HPC workloads

Intel® Xeon® 6 with E‑cores

- Architecture: Multi‑chip module

- Optimized for high core density, power efficiency, and scale‑out workloads

- Ideal for cloud, networking, and microservices environments

Intel® Xeon® 6+

- Architecture: Advanced multi‑chip module

- Combines many compute tiles with dedicated base and I/O tiles

- Designed for extremely high core counts and efficiency‑focused workloads

What Is the Difference?

Single‑Chip (Monolithic) Design

- All CPU cores, cache, and controllers are on one silicon die.

- Simpler internal layout

- Common in lower to mid‑core‑count processors

Multi‑Chip Module (MCM) Design

- Multiple silicon tiles are integrated into one processor package.

- Tiles are connected using high‑speed interconnects.

- Enables higher core counts, better manufacturing efficiency, and advanced packaging.

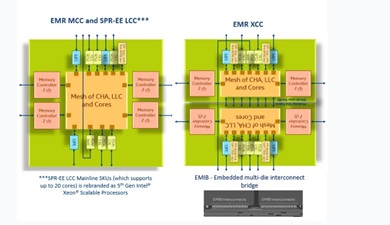

Architecture Overview (Visual)

Multi‑Chip Module (Tile‑Based) Architecture

- Multiple tiles inside one processor package

- Appears as one CPU to the system

Single‑Chip (Monolithic) Architecture

- One large die inside the processor package

Visual Comparison:

Quick Reference

| Processor Family | Architecture |

|---|---|

| 4th Gen Intel® Xeon® Scalable | Multi‑chip module |

| 4th Gen Intel® Xeon® Scalable | Single‑chip or MCM (model-dependent) |

| Xeon® 6 – Granite Rapids | Multi‑chip module |

| Xeon® 6 – Sierra Forest | Multi‑chip module |

| Xeon® 6+ – Clearwater Forest | Multi‑chip module |

Key Takeaway

Intel® Xeon® processors are not all built the same way.

Newer generations—especially Intel® Xeon® 6 and later—use multi‑chip module architectures to deliver higher scalability, efficiency, and performance across a wide range of workloads.

Note: It's important to note that the specifications can change with each new generation of processors, so for the most up-to-date information, you should refer to the latest Intel® Product Specifications.