A newer version of this document is available. Customers should click here to go to the newest version.

1. About the GTS CPRI PHY FPGA IP

2. Getting Started

3. GTS CPRI PHY IP Parameter Settings

4. Functional Description

5. Interface Signals

6. GTS CPRI PHY IP Registers

7. GTS CPRI PHY IP Troubleshooting

8. GTS CPRI PHY Intel FPGA IP User Guide Archives

9. Document Revision History for the GTS CPRI PHY Intel FPGA IP User Guide

5.1. GTS CPRI PHY IP Clock Signals

5.2. GTS CPRI PHY IP Reset Signals

5.3. GTS CPRI PHY IP TX MII (64b/66b)

5.4. GTS CPRI PHY IP RX MII (64b/66b)

5.5. GTS CPRI PHY IP Status Interface for 64b/66b Line Rate

5.6. GTS CPRI PHY IP TX Interface (8b/10b)

5.7. GTS CPRI PHY IP RX Interface (8b/10b)

5.8. GTS CPRI PHY IP Status Interface for 8b/10b Line Rate

5.9. GTS CPRI PHY IP Serial Interface

5.10. GTS CPRI PHY Reconfiguration Interface

5.11. GTS CPRI PHY IP Datapath and PMA Avalon Memory-Mapped Interface

3. GTS CPRI PHY IP Parameter Settings

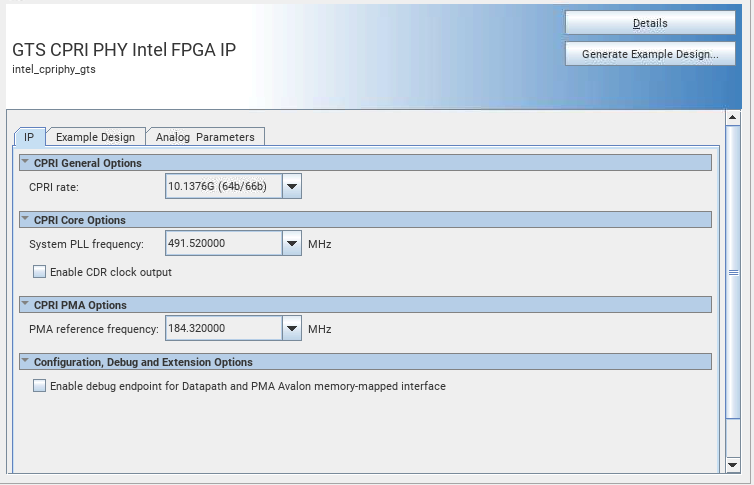

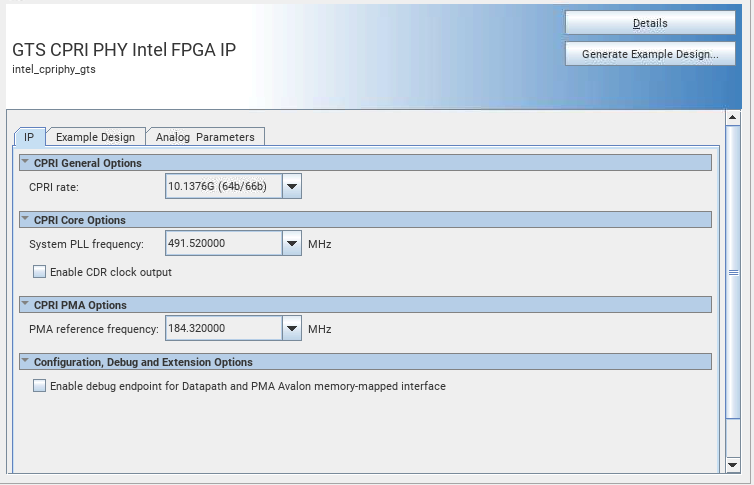

You customize the IP by specifying parameters in the IP parameter editor.

Figure 4. GTS CPRI PHY IP Parameter Editor

| Parameter | Supported Values | Default Setting | Description |

|---|---|---|---|

| CPRI General Options | |||

| CPRI Rate |

|

10.1376G (64b/66b) | Selects the CPRI data rate.

|

| CPRI Core Options | |||

| System PLL Frequency | 491.52 MHz or 805.664062 MHz | 491.52 MHz | Select the system PLL frequency for your IP.

|

| Enable CDR Clock Output |

|

Off | Turn on this parameter to enable CDR reference clock output. o_cdr_divclk= refclk/N Refer to the Required Clock Frequencies for exact values. |

| CPRI PMA Options | |||

| PMA Reference Frequency |

|

184.32 MHz | Reference clock frequency support:

|

| Configuration, Debug, and Extension Option | |||

| Enable Debug Endpoint for Datapath and PMA Avalon Memory-Mapped Interface |

|

Off | When turned on, the GTS CPRI PHY Intel FPGA IP includes an embedded Debug Endpoint that internally connects the Avalon memory-mapped agent interface. The Debug Endpoint can access the reconfiguration space of the datapath and PMA interface block. It can perform certain tests and debug functions through the JTAG using the System Console. This option may require that you include a jtag_debug link in the system. |

Related Information