R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683544

Date

12/04/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express

2. Quick Start Guide

3. R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express* Design Example User Guide Archives

4. Document Revision History for the R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express* Design Example User Guide

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

2.3.2.3. PIO Design Example Testbench

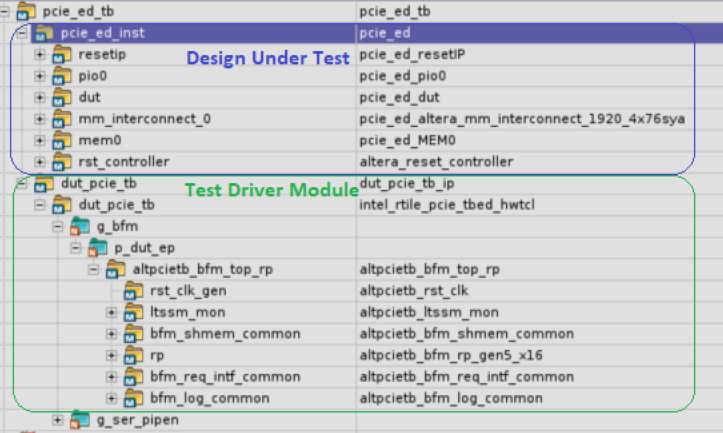

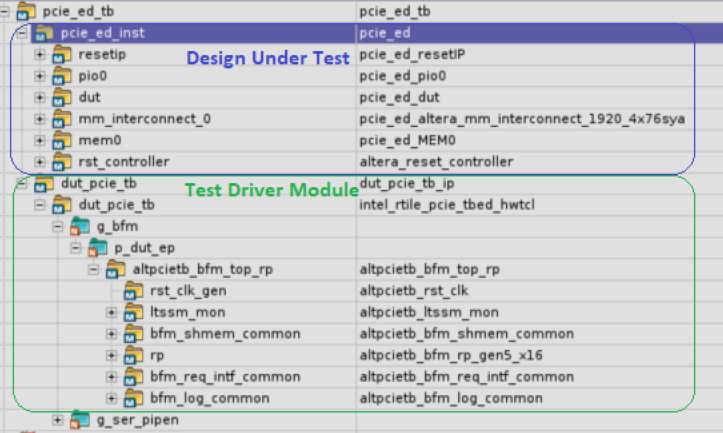

The figure below shows the PIO design example simulation design hierarchy. The tests for the PIO design example are defined with the apps_type_hwtcl parameter set to 3. The tests run under this parameter value are defined in ebfm_cfg_rp_ep_rootport, find_mem_bar and downstream_loop.

Figure 24. PIO Design Example Simulation Design Hierarchy

The testbench starts with link training and then accesses the configuration space of the IP for enumeration. A task called downstream_loop (defined in the Root Port PCIe BFM altpcietb_bfm_rp_gen5_x16.sv) then performs the PCIe link test. This test consists of the following steps:

- Issue a memory write command to write a single dword of data into the on-chip memory behind the Endpoint.

- Issue a memory read command to read back data from the on-chip memory.

- Compare the read data with the write data. If they match, the test counts this as a Pass.

- Repeat Steps 1, 2 and 3 for 10 iterations.

The first memory write takes place around 219 us. It is followed by a memory read at the Avalon® -ST RX interface of the R-Tile Hard IP for PCIe. The Completion TLP appears shortly after the memory read request at the Avalon® -ST TX interface.

Note: In the 2x8 design example, memory read and memory write transactions are simulated on Port 0 only.