Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

1/27/2025

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.2.5.1. Build and Install Netdev Driver

3.5.2.5.2. Enable VFs if SRIOV is Supported

3.5.2.5.3. Configure the Number of Channels Supported on the Device

3.5.2.5.4. Configure the MTU Value

3.5.2.5.5. Configure the Device Communication

3.5.2.5.6. Configure Transmit Queue Selection Mechanism

3.5.2.5.7. Test Procedure by Using Name Space Environment

3.5.2.5.8. PIO Test

3.5.2.3.3.3. BAM Test

If the BAM support is enabled on hardware, enable the following flag in common/mk/common.mk:

__cflags += -DIFC_PIO_256 → 256b read/write operations on PIO BAR

__cflags += -DIFC_PIO_128 → 128b read/write operations on PIO BAR

For PIO using Bypass with BAM/BAS user mode, you are required to change the define parameter to undef: #undef IFC_QDMA_INTF_ST(software/user/common/include/mcdma_ip_params.h)

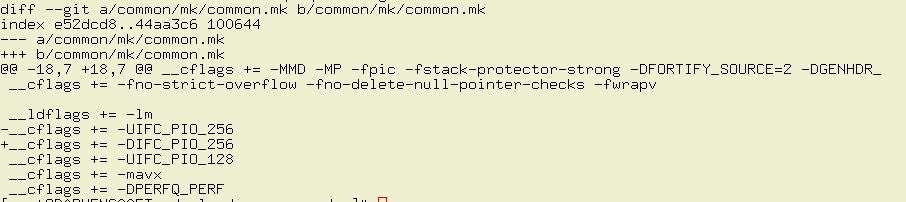

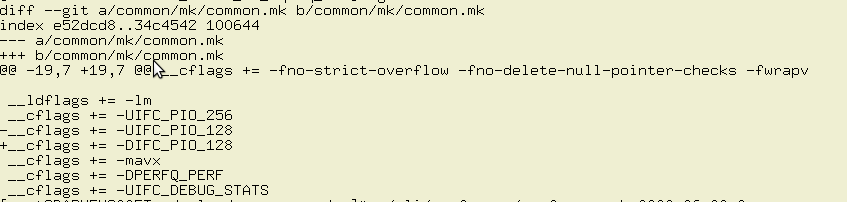

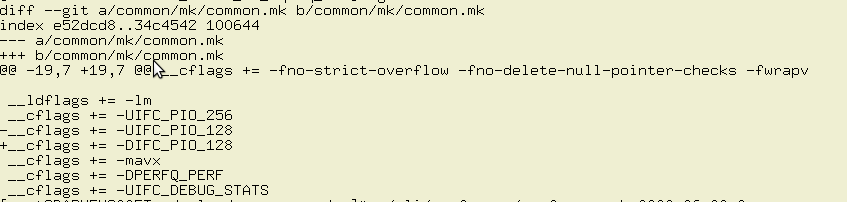

To enable 256 bit read/write operations, this is the difference in common.mk:

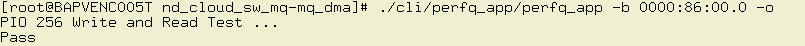

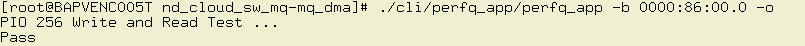

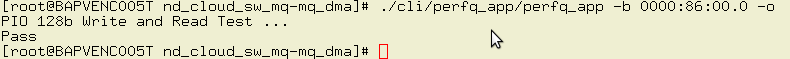

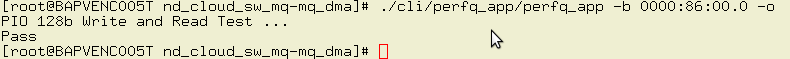

Command: ./cli/perfq_app/perfq_app -b 0000:86:00.0 -o

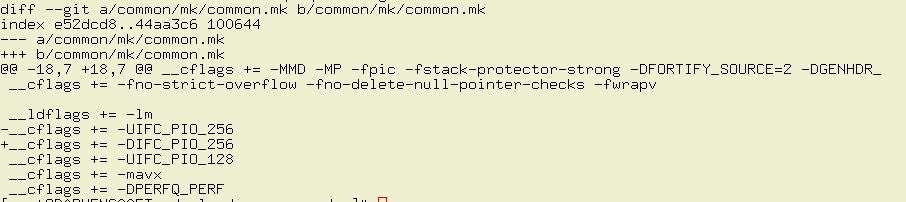

To enable 128 bit read/write operations:

Command:

To test the PIO/BAM performance, please use the following command:

Command:

[root@bapvemb005t perfq_app]# ./perfq_app -b 0000:01:00.0 --bam_perf -o PIO 64 Write and Read Perf Test ... Total Bandwidth: 0.14GBPS Pass [root@bapvemb005t perfq_app]#

- By default BAM/BAS, BAR is 2. If DMA Hardware supports both BAM/BAS and BAR numbers are different, then pass BAR number parameter as below:

--bar=2 for BAM

--bar=0 for BAS

-

For example:

./perfq_app -b 0000:01:00.0 --bam_perf -o --bar=2

- Performance mode of BAM tries to send the data for 10 seconds and calculates the bandwidth

- PIO 256b test may display fail because of the reason that 2k memory only enabled in device and PIO test trying to access the memory > 2k